### 二級D觸發器應用于同步器,減少亞穩態

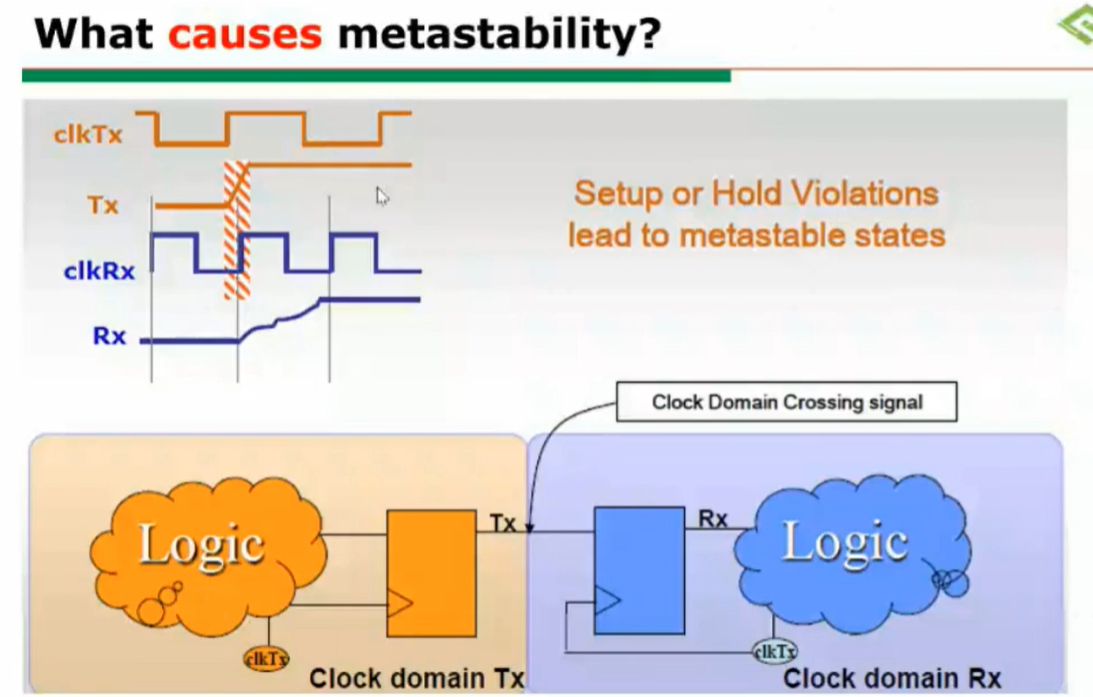

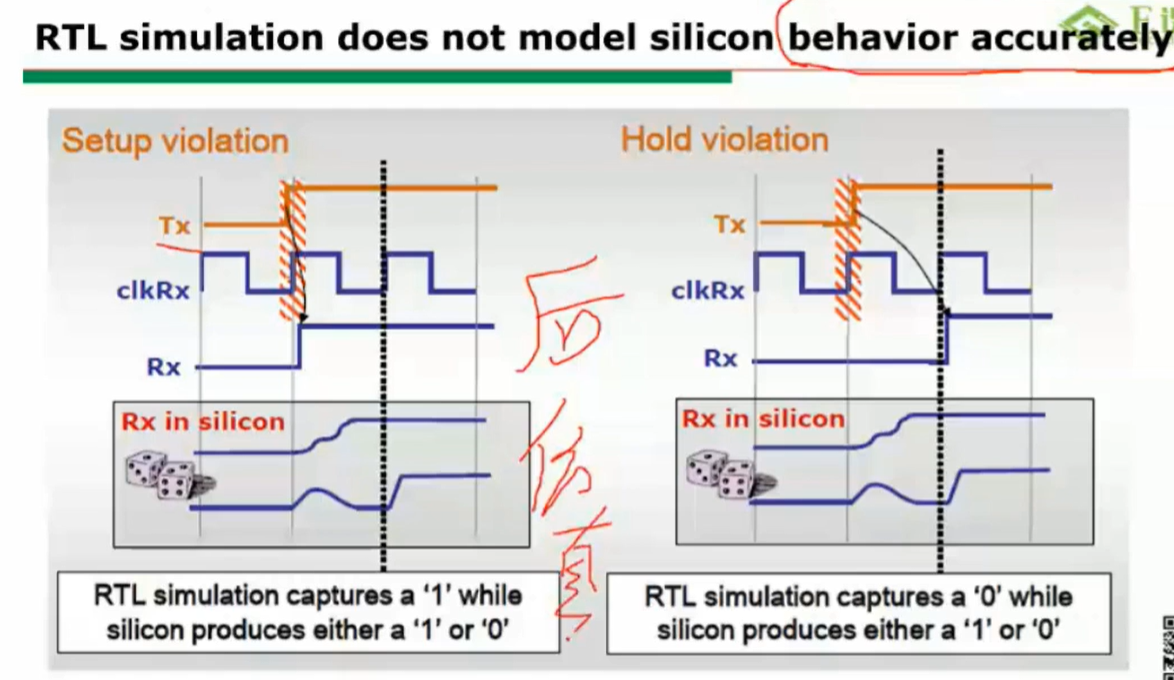

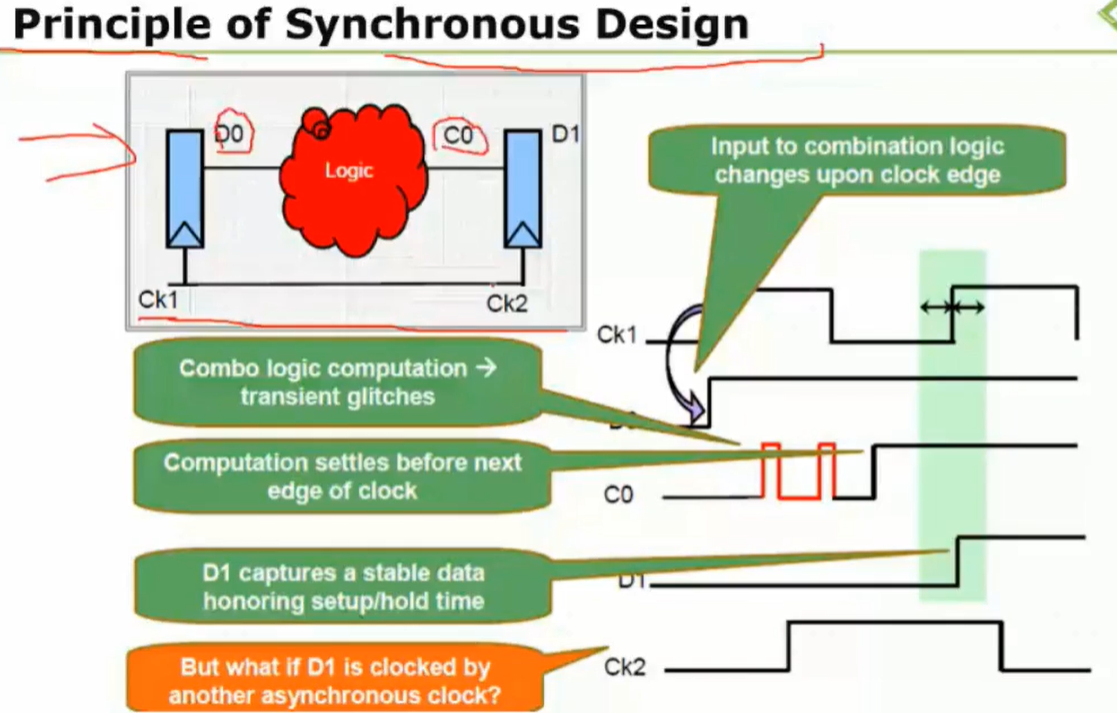

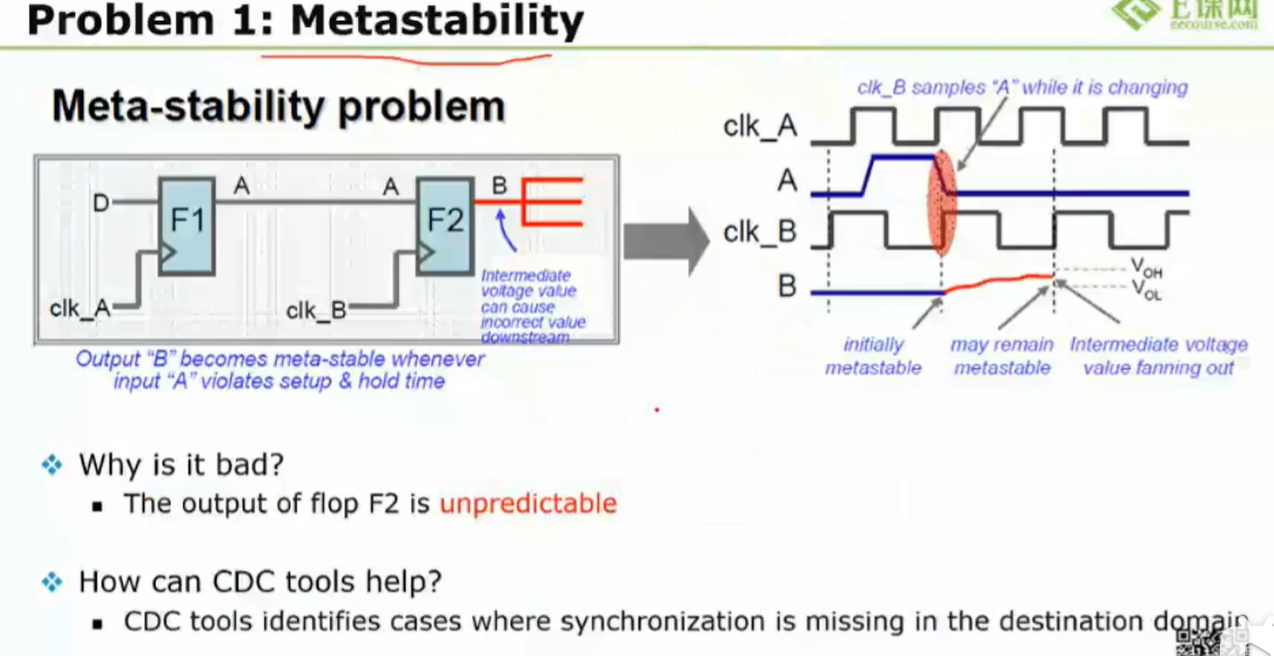

**建立時間**(Tsu:set up time)是指在時鐘沿到來之前數據從不穩定到穩定所需的時間,如果建立的時間不滿足要求那么數據將不能在這個時鐘上升沿被穩定的打入觸發器;

**保持時間**(Th:hold time)是指數據穩定后保持的時間,如果保持時間不滿足要求那么數據同樣也不能被穩定的打入觸發器。

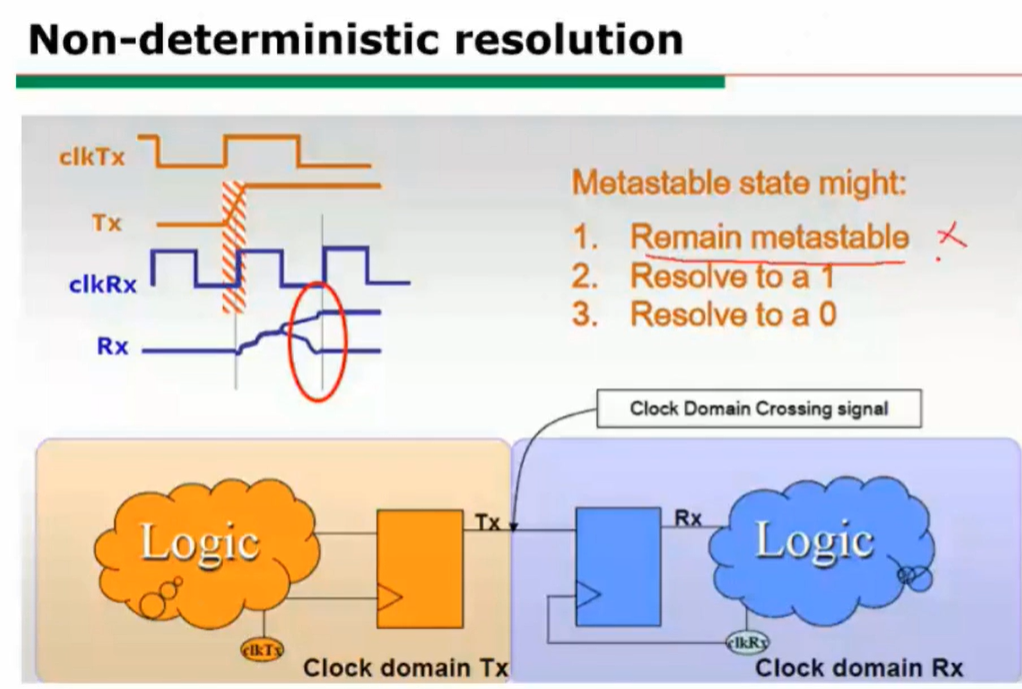

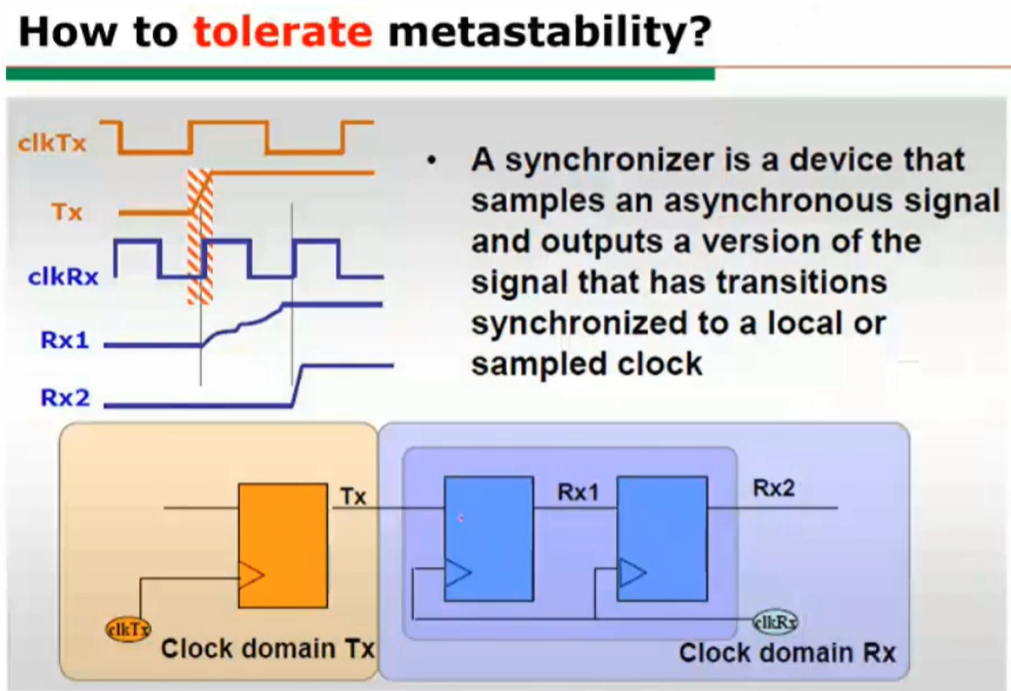

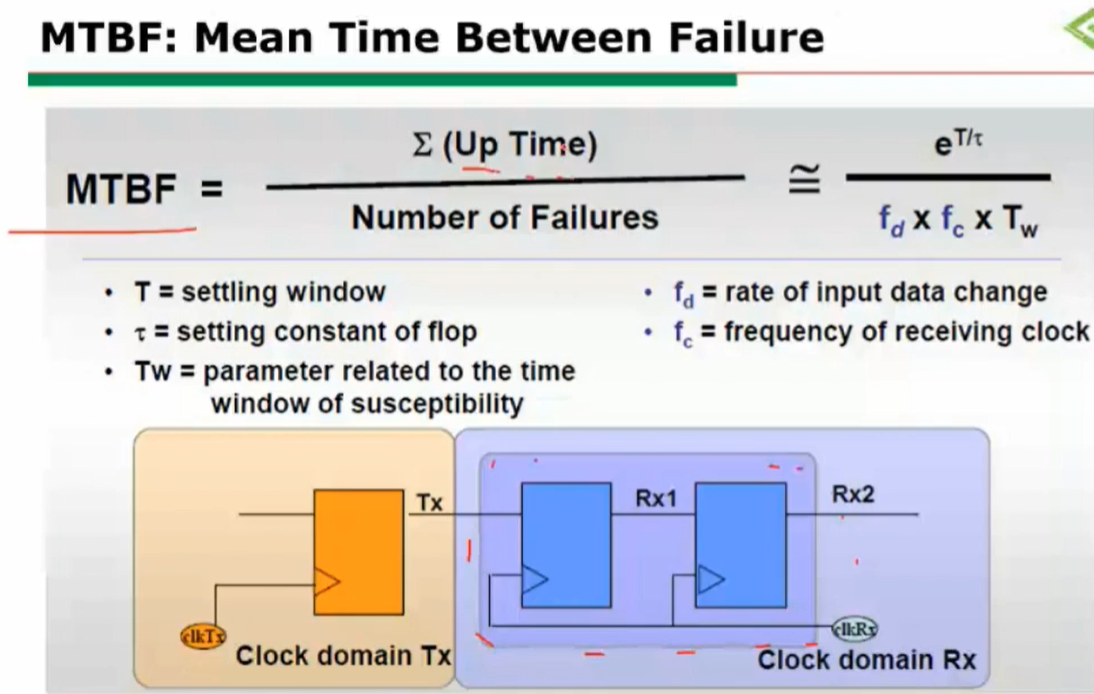

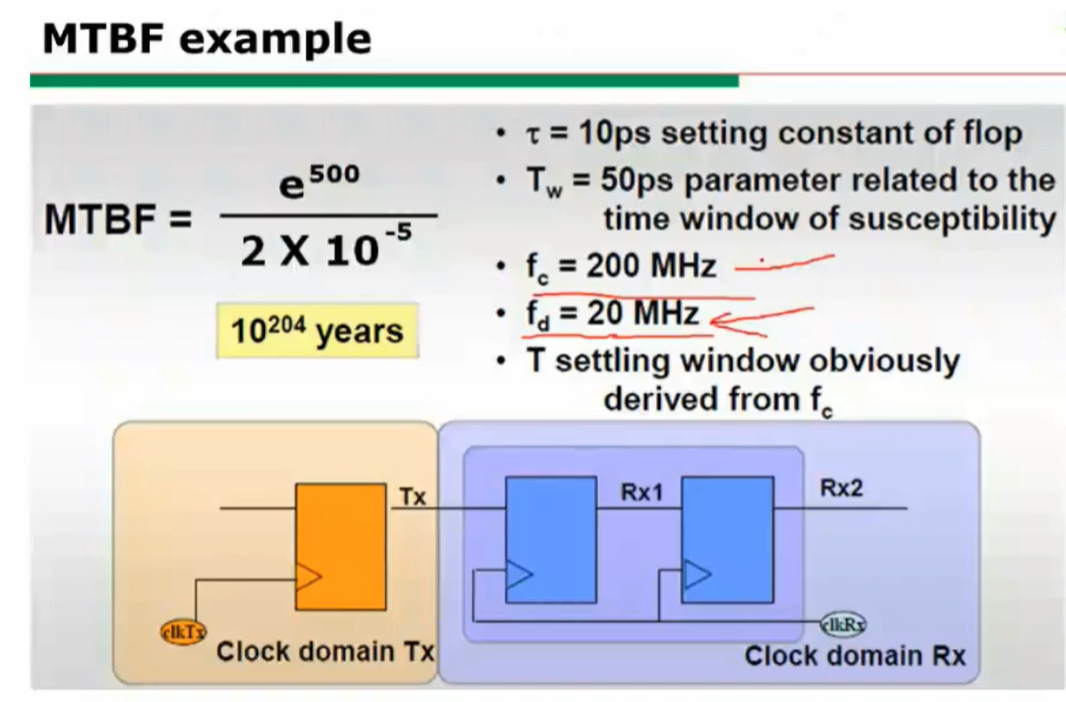

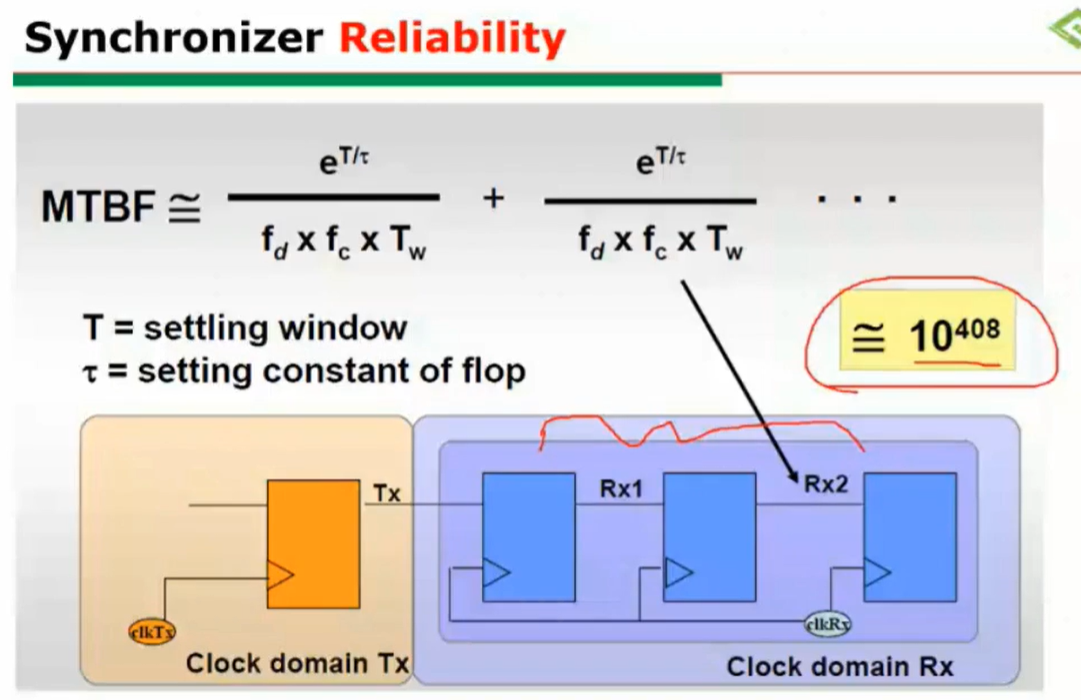

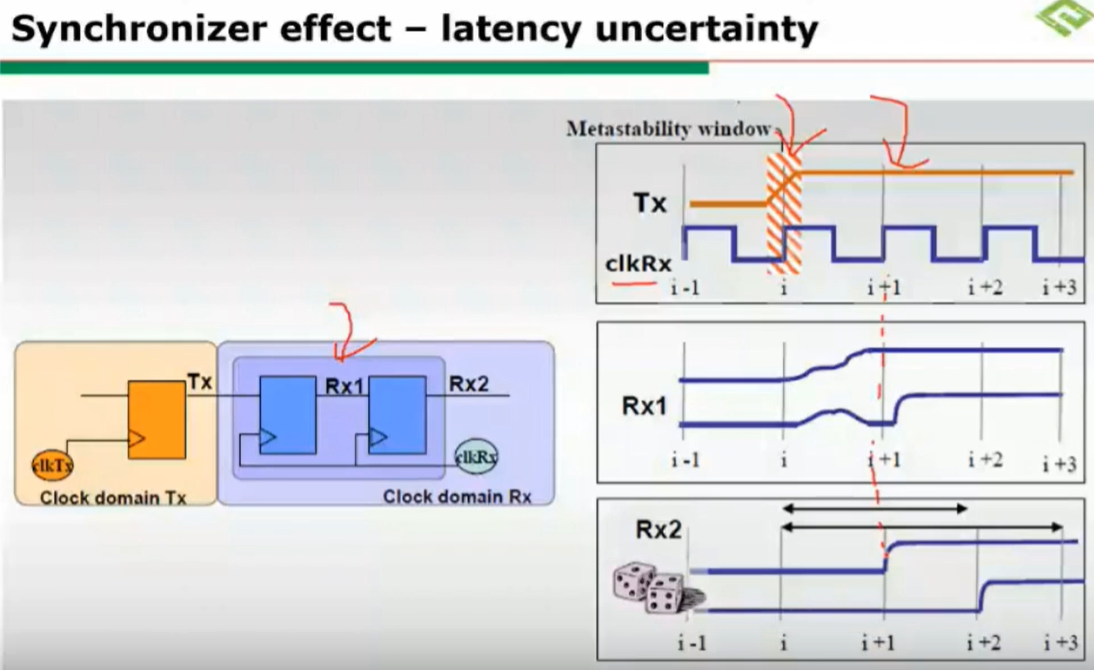

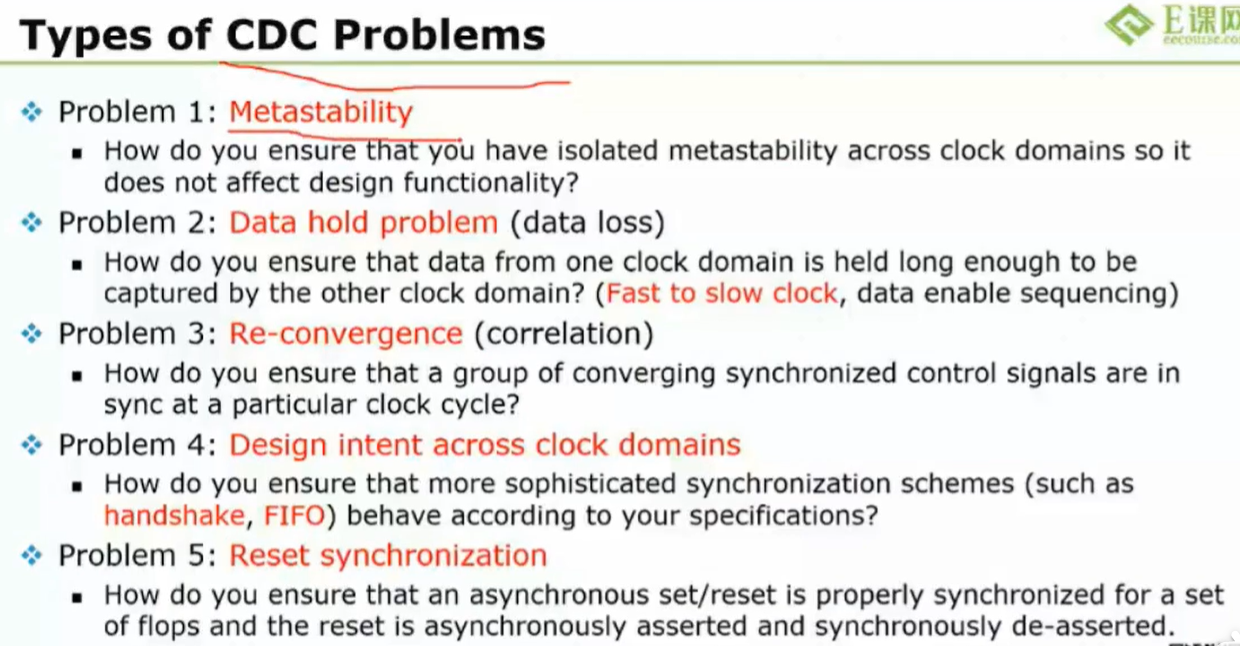

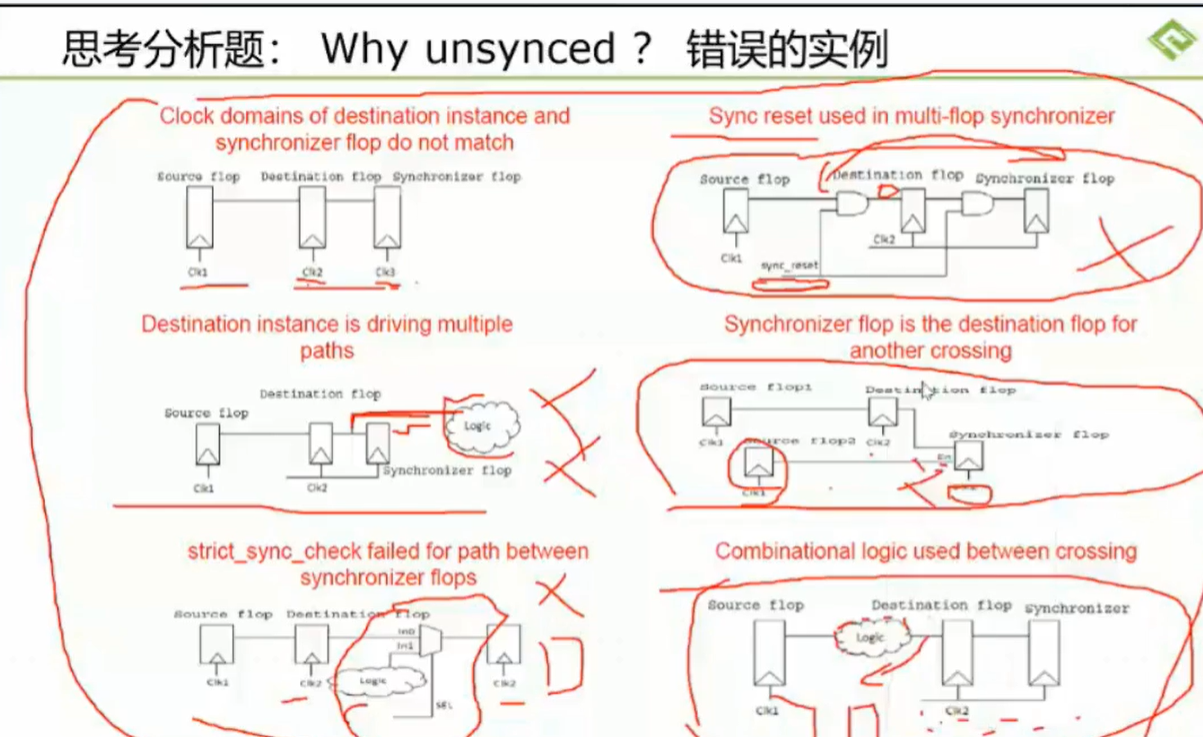

當第一級觸發器采樣異步輸入之后,允許輸出出現的亞穩態可以長達一個周期,**在這個周期內,亞穩態特性減弱**。在第二個時鐘沿到來時,第二級同步器采樣,之后才把該信號傳遞到內部邏輯中去。**第二級輸出是穩定且已被同步了的。如果在第二級采樣時保持時間不夠,第一級的輸出仍然處于很強的亞穩態,將會導致第二級同步器也進入亞穩態,但這種故障出現的概率比較小。**

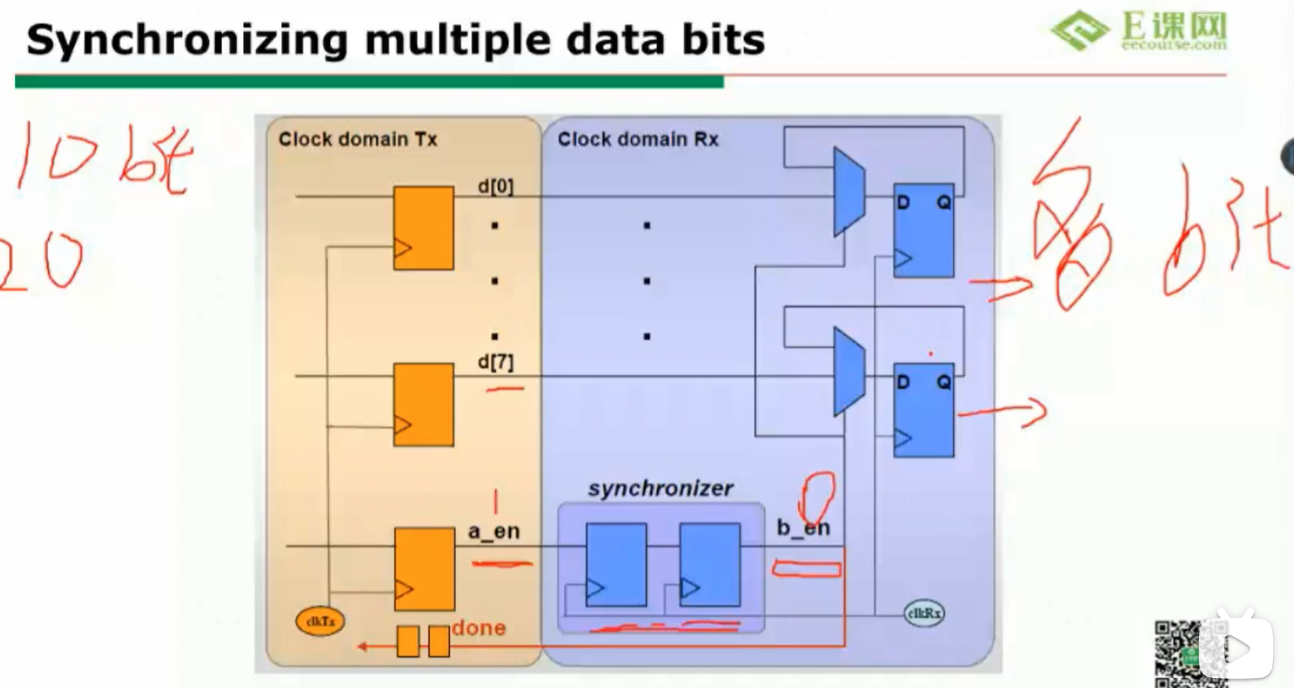

一般情況下,兩級同步器總體的故障概率是一級同步器故障概率的平方。**在大部分的同步化設計中,兩級同步器足以消除所有可能的亞穩態了。**

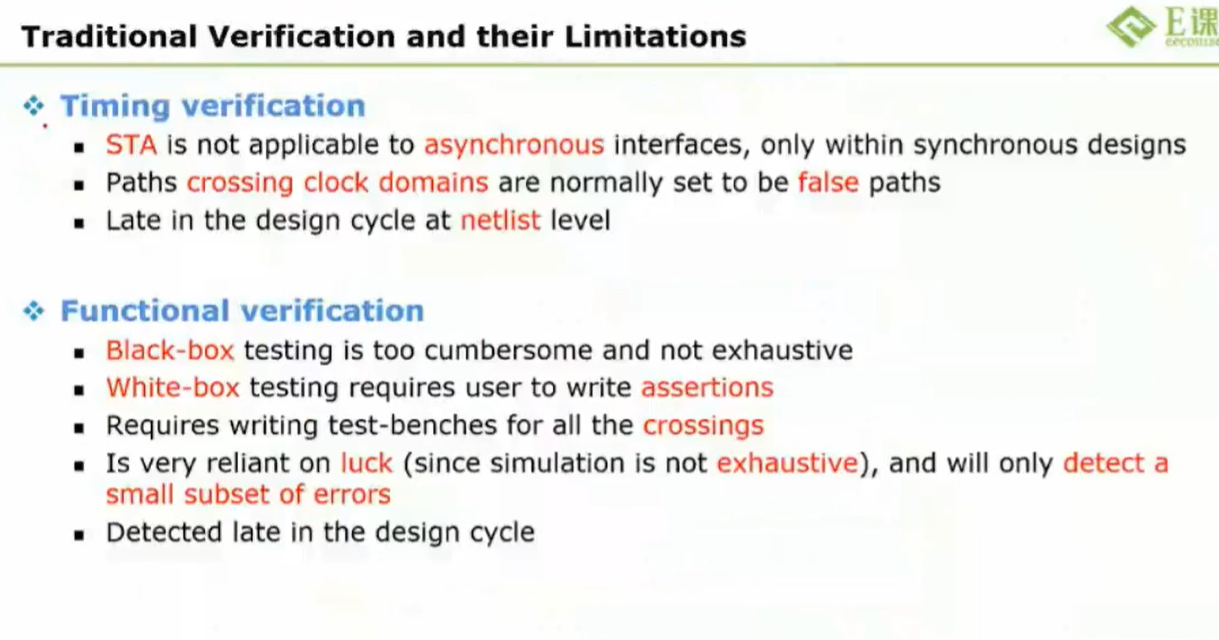

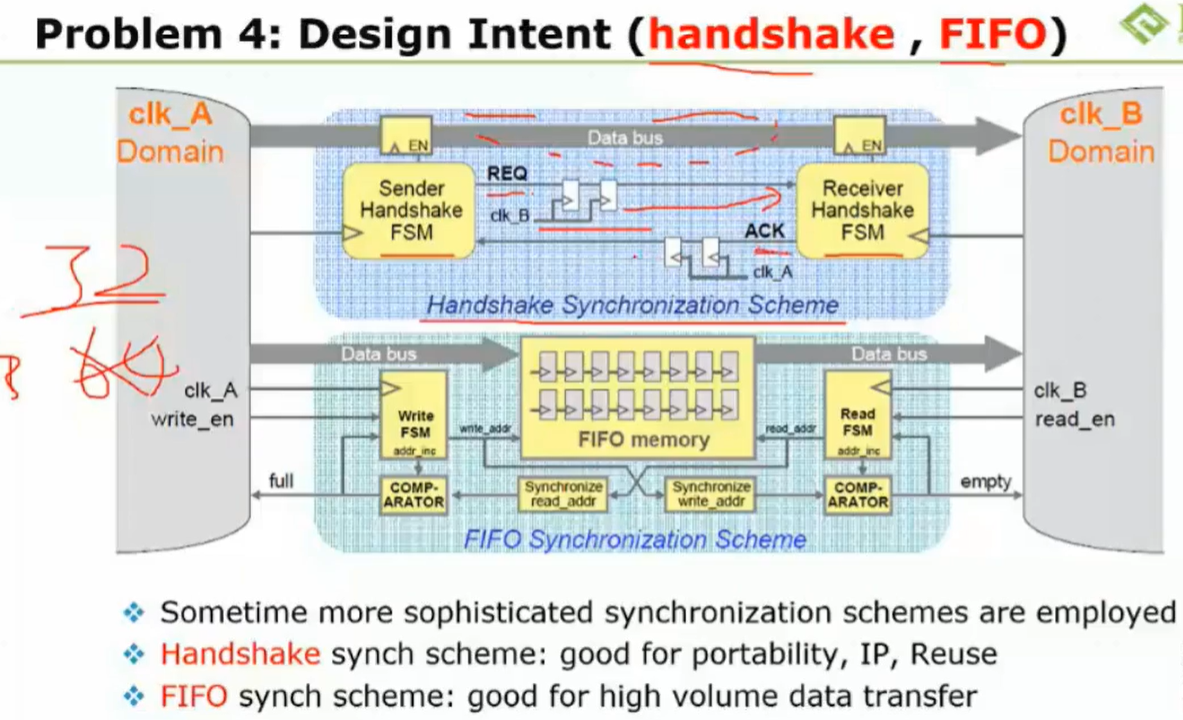

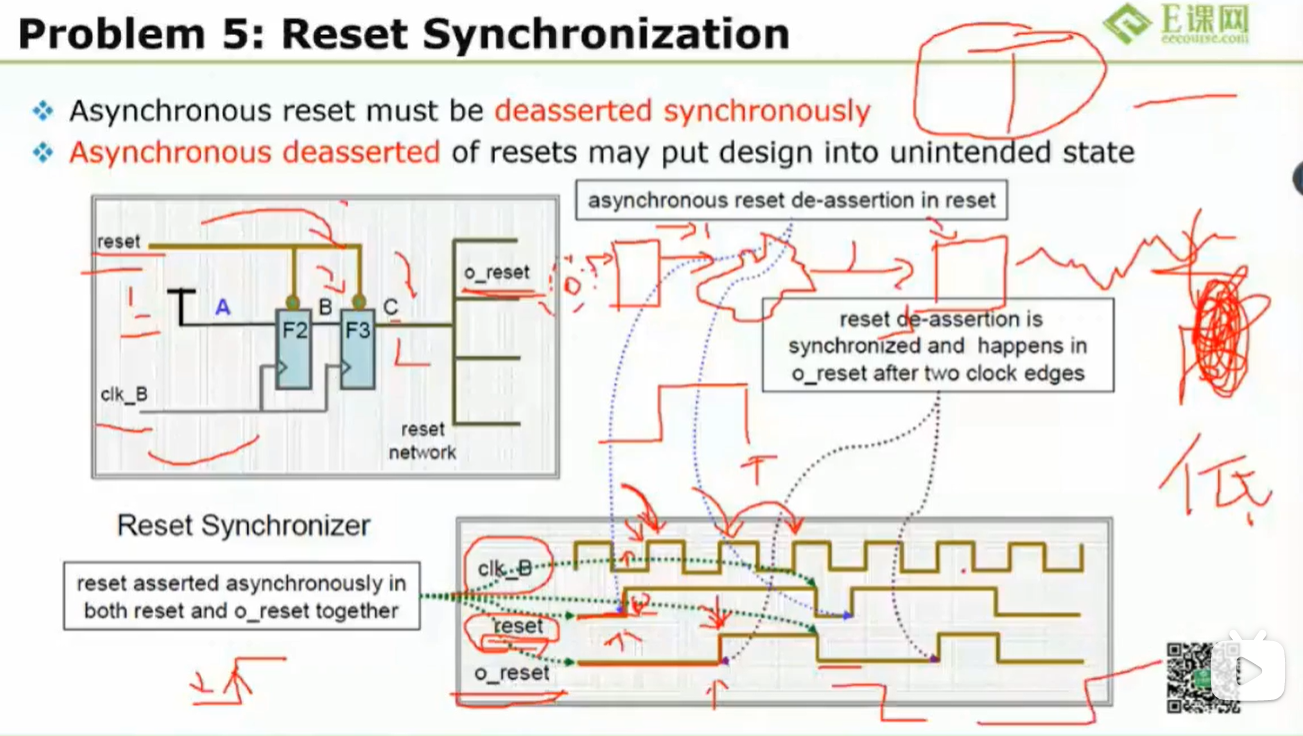

synchronous有一個時鐘域,

asynchronous 有多個時鐘域,會出現跨時鐘域的問題

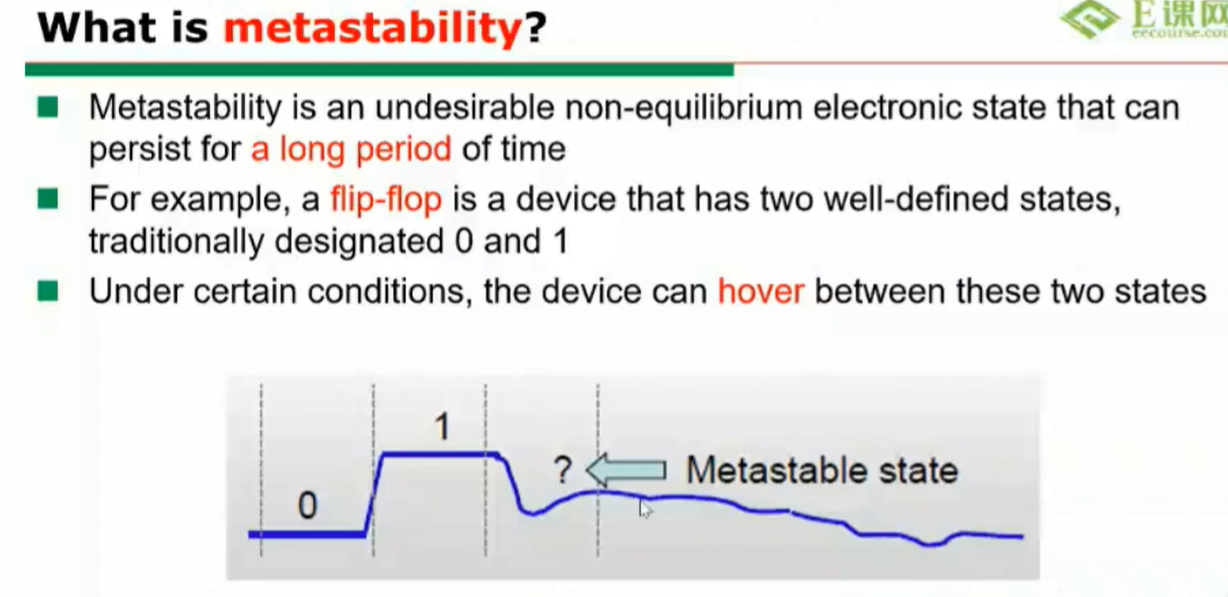

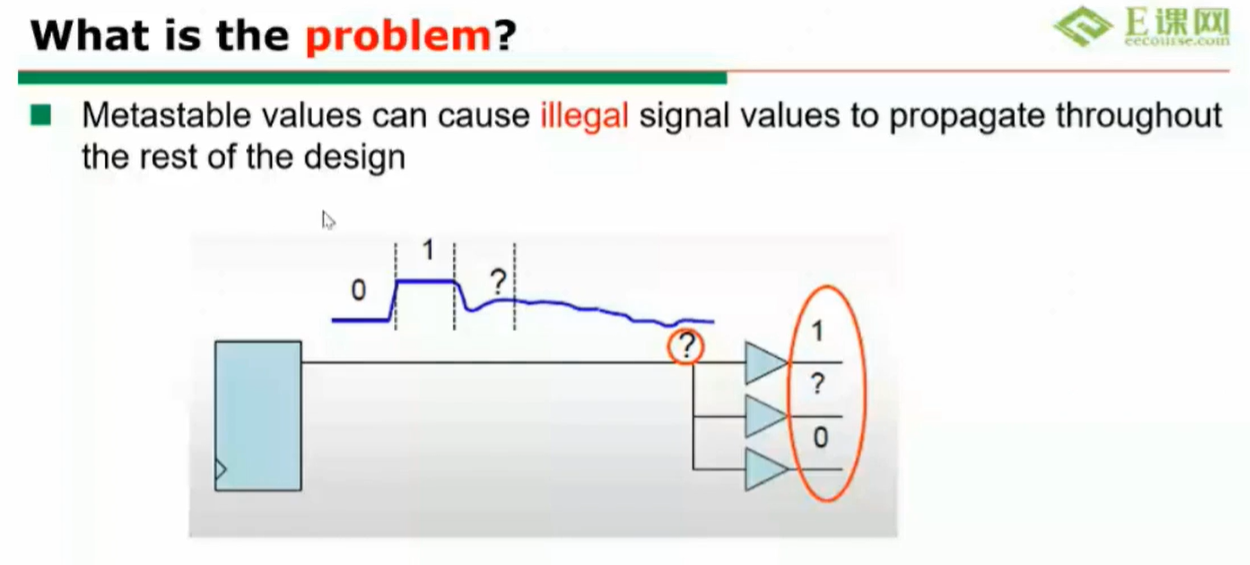

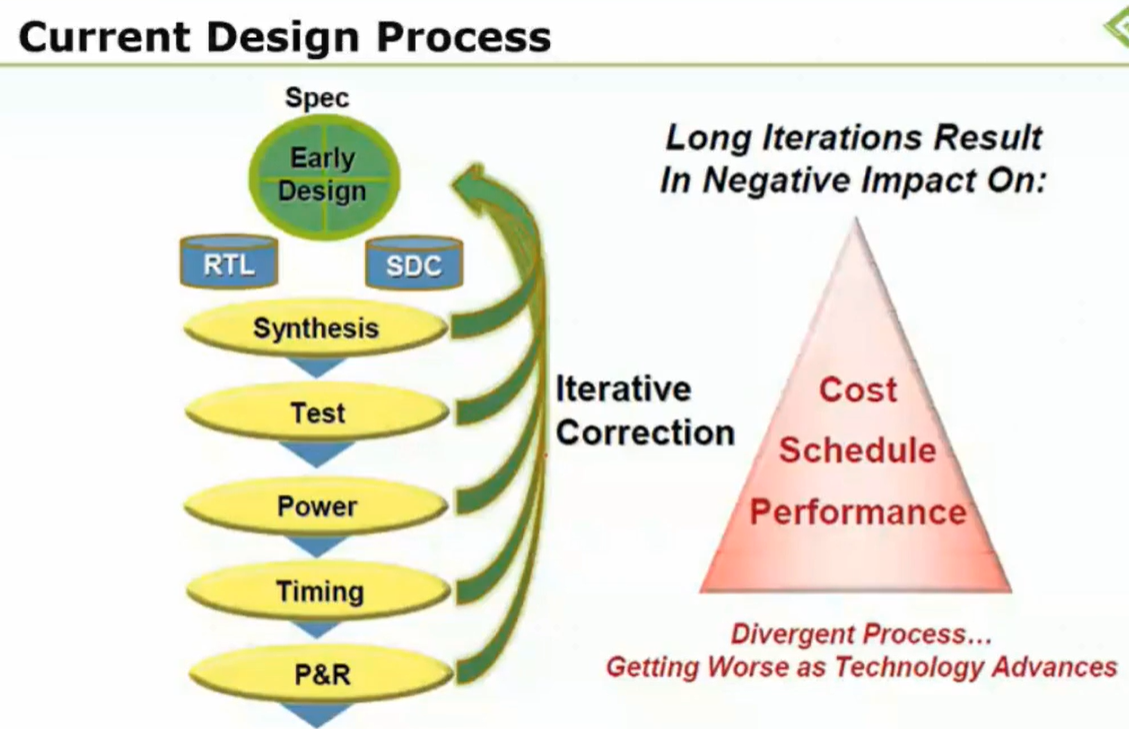

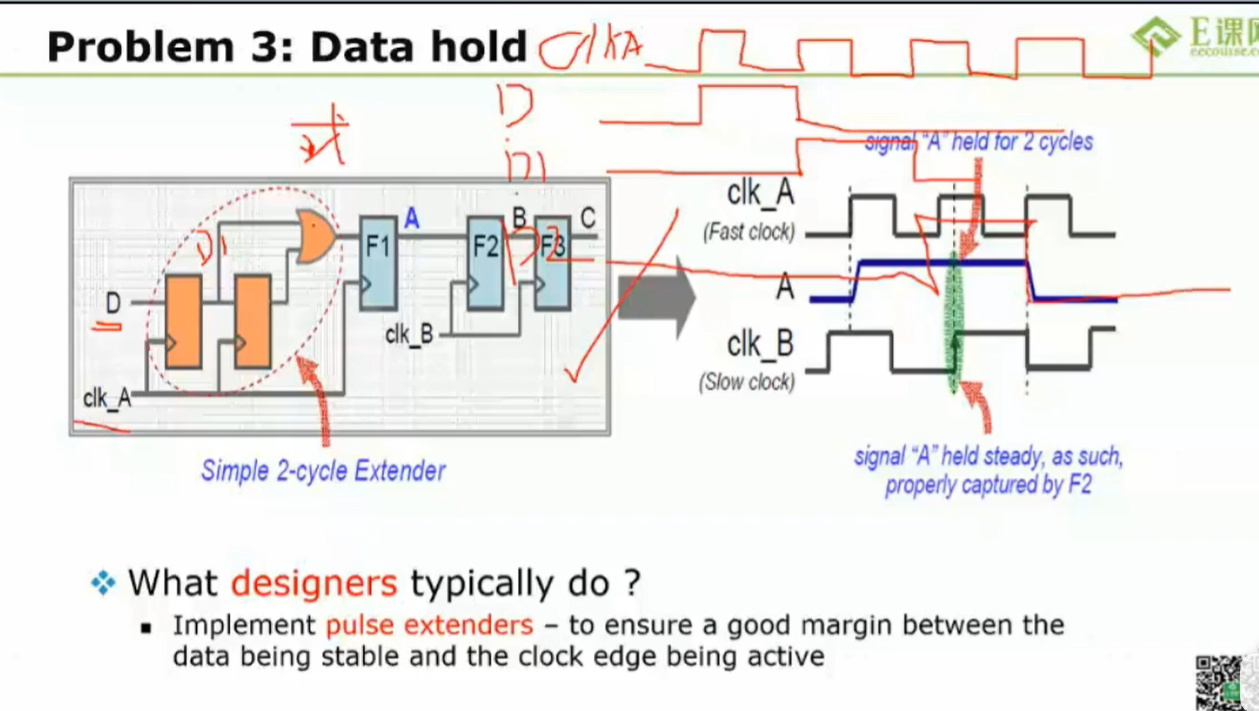

延時太長,建立時間和保持時間違例;

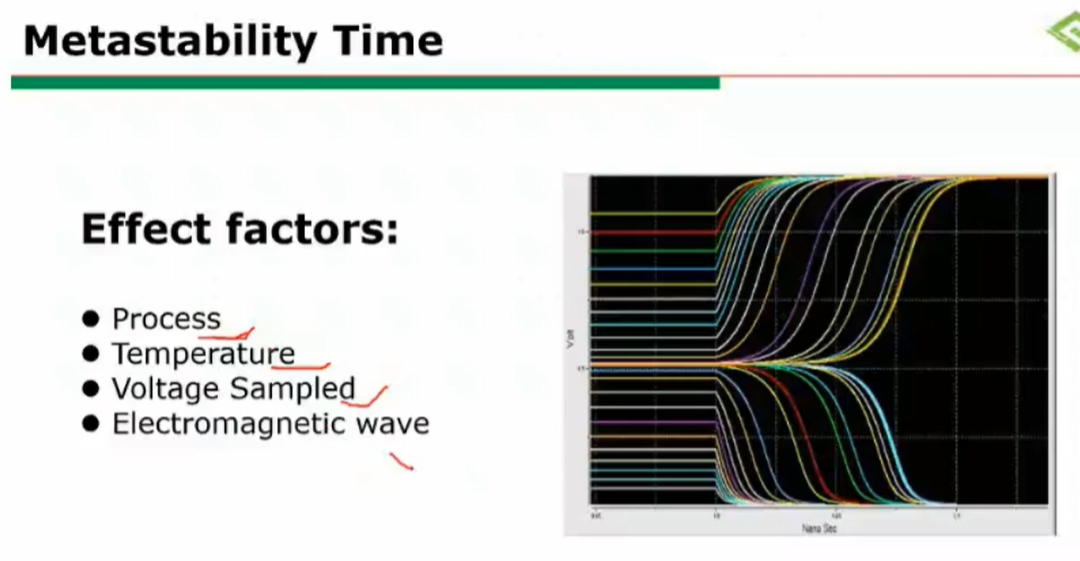

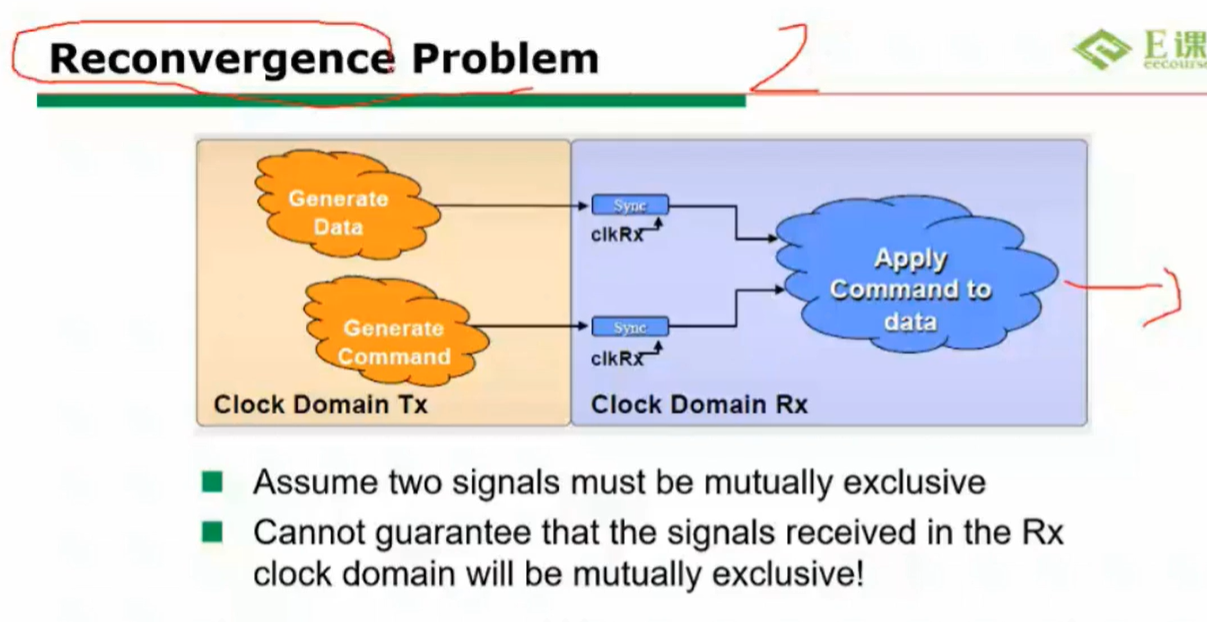

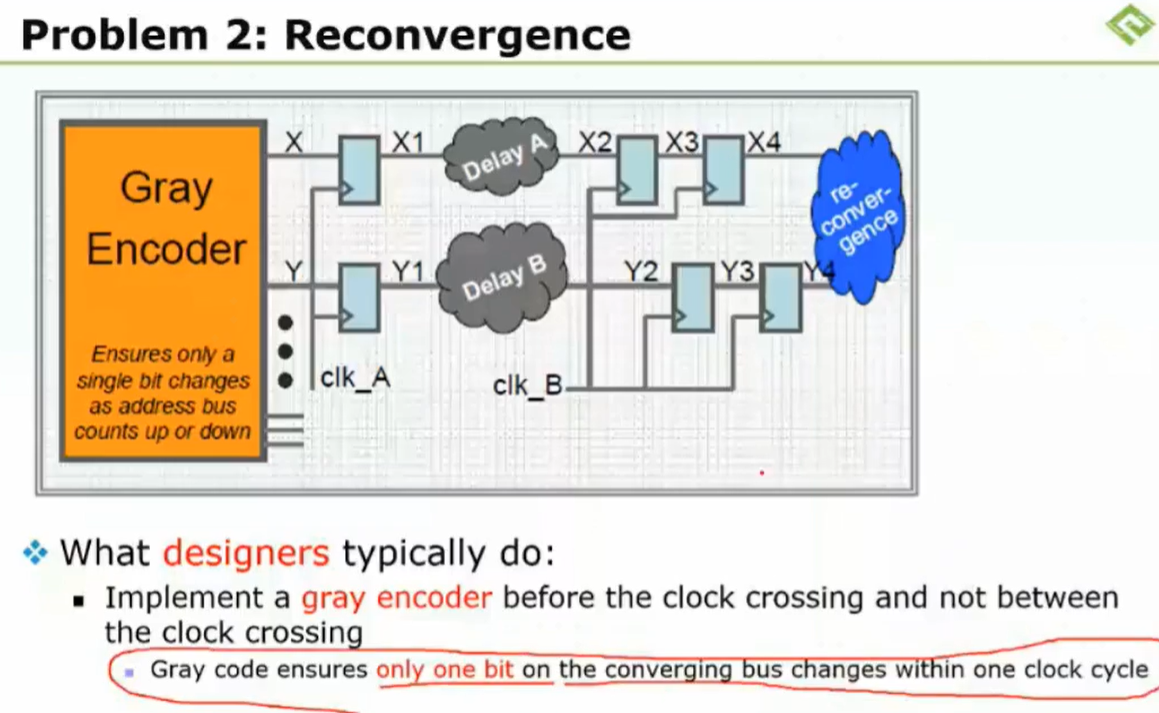

造成亞穩態,clock reconvergence pessimism是launching時鐘路徑和capturing時鐘路徑的延時差值,它發生在時鐘切換的時候,是基于library通過查找LUT得到的

- 空白目錄

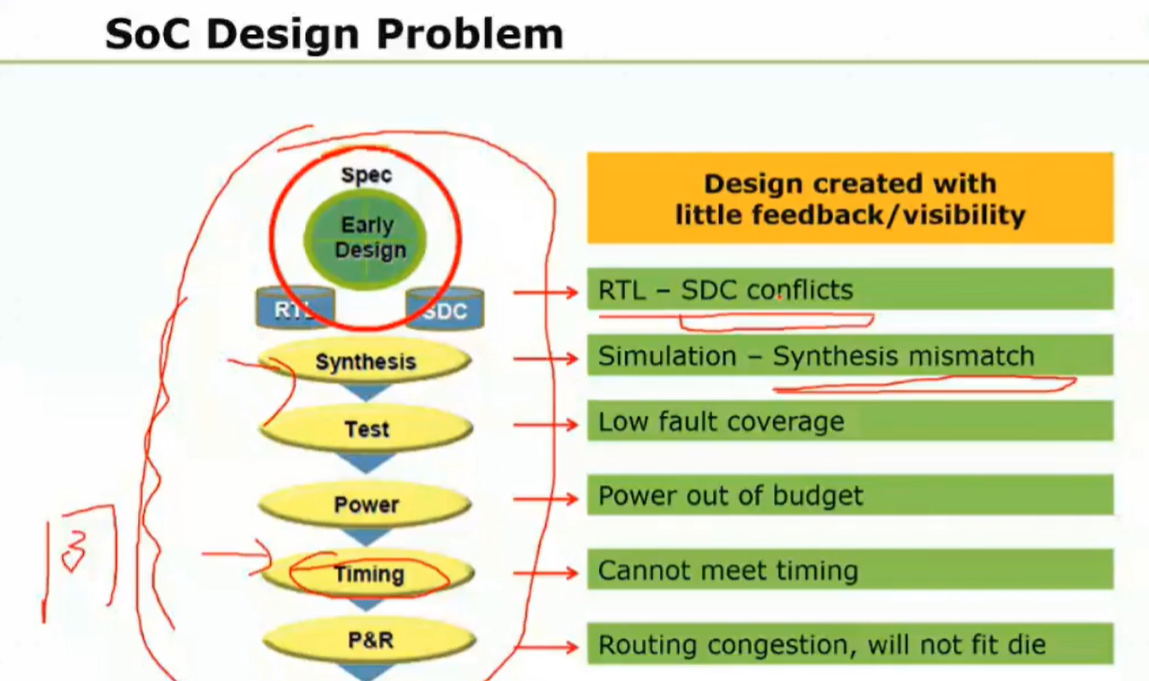

- 任務01:數字IC設計流程_

- 任務02:數字前端設計工程師就業班概述_

- 任務03:VNC服務器使用說明_

- 任務07:數字電路基礎_

- 任務09:邏輯綜合工具Design Compiler的使用_

- 任務10:數字電路基礎-時序邏輯基礎

- 任務20: 經典組合和數字電路的設計_

- 任務21:有限狀態機的寫法_

- 任務25:CDC_Metastability(亞穩態)_

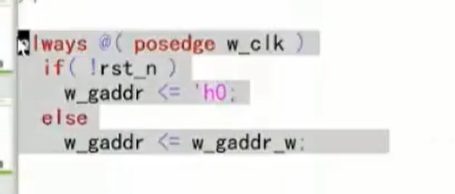

- 任務22:同步fifo-異步fifo的設計_

- 任務23:同步FIFO設計方法2介紹與仿真

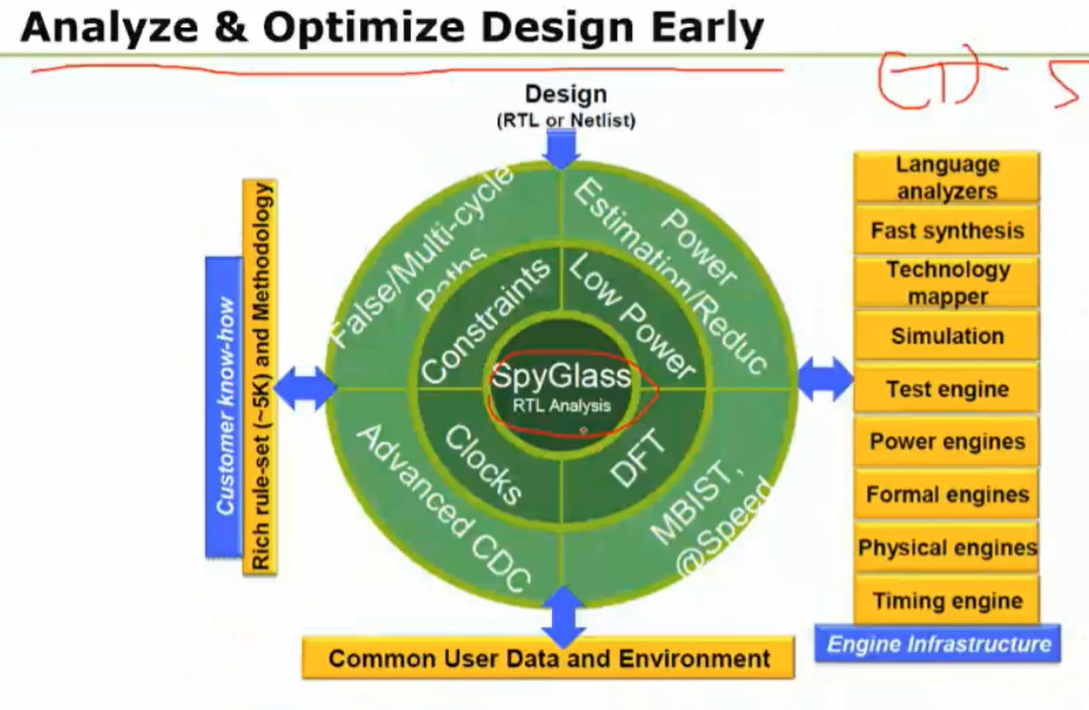

- 任務28:Spyglass的基礎使用_

- 任務24:異步FIFO的設計_

- 任務29:Spyglass的基本使用-2_

- 任務11:邏輯仿真工具VCS的使用-Makefile_

- 任務15:Verilog Systemverilog - 數據類型_

- 任務13:邏輯綜合工具-DC實操