要將快時鐘域的脈沖信號同步到慢時鐘域的信號常采用握手的機制實現,所以該電路又常被稱為握手電路,其設計思路為:首先在慢時鐘域下將快時鐘域的脈沖轉換為電平信號,然后把電平信號同步到快時鐘域,同步完成后的信號要反饋回快時鐘域,快時鐘域接收到該信號后給控制信號,原來的電平信號被拉低。

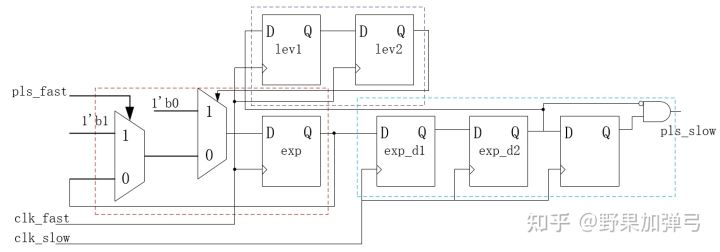

圖 :快時鐘域到慢時鐘域準換電路

如圖所示,pls\_fast為輸入的快時鐘域的脈沖信號,紅框部分是脈沖轉電平結構,exp寄存器輸出的電平信號被exp\_d1和exp\_d2同步到慢時鐘域(藍框部分),exp\_d2再打一拍造出慢時鐘域的脈沖信號。exp\_d2信號需要反饋回快時鐘域,根據數字設計的基本原則,再采用兩級同步器lev1和lev2(紫框部分)將信號抓取回來作為控制信號將原來高電平信號拉低,握手完成。

~~~verilog

module pls_sync_f2s(

rst_n ,

clka ,

clkb ,

pls_a ,

pls_b

);

//parametr

parameter DLY = 1 ;

//input output

input rst_n ;

input clka ;

input clkb ;

input pls_a ;//pluse in

output pls_b ;//pluse out

//-----------------------------

//--signal

//-----------------------------

reg exp ;

reg exp_d1 ;

reg exp_d2 ;

reg exp_d3 ;

reg lev1 ;

reg lev2 ;

//-----------------------------

//--main circuit

//-----------------------------

//pluse 2 level

always@(posedge clka or negedge rst_n)

begin

if(!rst_n)

exp <= 1'b0 ;

else if(lev2)

exp <= #DLY 1'b0 ;

else if(pls_a)

exp <= #DLY 1'b1 ;

end

always@(posedge clka or negedge rst_n)

begin

if(!rst_n) begin

lev1 <= 1'b0 ;

lev2 <= 1'b0 ;

end

else begin

lev1 <= #DLY exp_d2 ;

lev2 <= #DLY lev1 ;

end

end

always@(posedge clkb or negedge rst_n)

begin

if(!rst_n) begin

exp_d1 <= 1'b0 ;

exp_d2 <= 1'b0 ;

exp_d3 <= 1'b0 ;

end

else begin

exp_d1 <= #DLY exp ;

exp_d2 <= #DLY exp_d1 ;

exp_d3 <= #DLY exp_d2 ;

end

end

assign pls_b = exp_d2 & (~exp_d3) ; //posedge pluse detect

endmodule

~~~

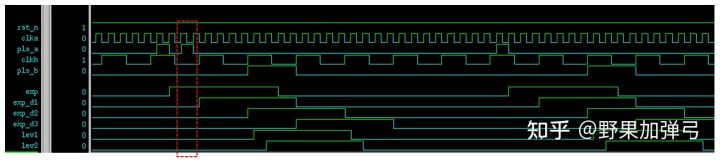

仿真波形如圖6所示。

## **快時鐘域到慢時鐘域轉換電路的局限性**

握手電路的局限性在于快時鐘域產生的脈沖信號的間隔不能太短,否則會造成慢時鐘域同步的脈沖丟失,如圖6所示,紅色方框內快時鐘域的脈沖沒有被同步到慢時鐘域。