AMBA (Advanced Microcontroller Bus Architecture) 高級處理器總線架構

```

AHB (Advanced High-performance Bus) 高級高性能總線

ASB (Advanced System Bus) 高級系統總線

APB (Advanced Peripheral Bus) 高級外圍總線

AXI (Advanced eXtensible Interface) 高級可拓展接口

```

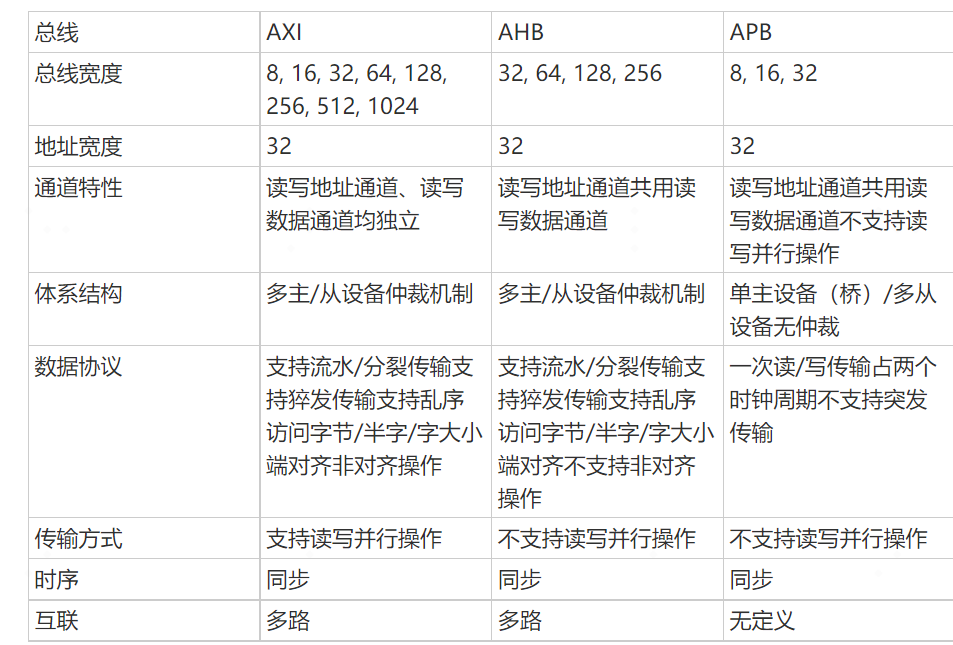

這些內容加起來就定義出一套為了高性能SoC而設計的片上通信的標準。 AHB主要是針對高效率、高頻寬及快速系統模塊所設計的總線,它可以連接如微處理器、芯片上或芯片外的內存模塊和DMA等高效率模塊。 APB主要用在低速且低功率的外圍,可針對外圍設備作功率消耗及復雜接口的最佳化。APB在AHB和低帶寬的外圍設備之間提供了通信的橋梁,所以APB是AHB或ASB的二級拓展總線。 AXI:高速度、高帶寬,管道化互聯,單向通道,只需要首地址,讀寫并行,支持亂序,支持非對齊操作,有效支持初始延遲較高的外設,連線非常多。

1.1.3AHB總線

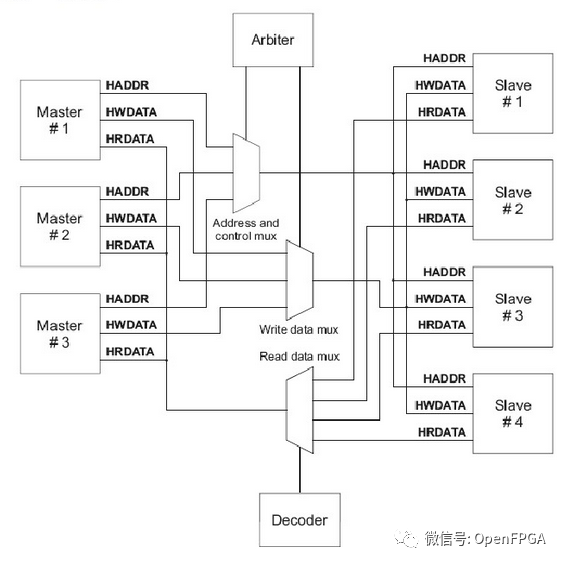

AHB的組成 Master:能夠發起讀寫操作,提供地址和控制信號,同一時間只有1個Master會被激活。 Slave:在給定的地址范圍內對讀寫操作作響應,并對Master返回成功、失敗或者等待等狀態。 Arbiter:負責保證總線上一次只有1個Master在工作。仲裁協議是規定的,但是仲裁算法可以根據應用決定。 Decoder:負責對地址進行解碼,并提供片選信號到各Slave。 每個AHB都需要1個仲裁器和1個中央解碼器。

AHB的組成 AHB基本信號 HADDR:32位系統地址總線 HTRANS:M指示傳輸狀態,NONSEQ、SEQ、IDLE、BUSY HWRITE:傳輸方向1-寫,0-讀 HSIZE:傳輸單位 HBURST:傳輸的burst類型 HWDATA:寫數據總線,從M寫到S HREADY:S應答M是否讀寫操作傳輸完成,1-傳輸完成,0-需延長傳輸周期。需要注意的是HREADY作為總線上的信號,它是M和S的輸入;同時每個S需要輸出自HREADY。所以對于S會有兩個HREADY信號,一個來自總線的輸入,一個自己給到多路器的輸出。 HRESP:S應答當前傳輸狀態,OKAY、ERROR、RETRY、SPLIT。 HRDATA:讀數據總線,從S讀到M。 AHB基本傳輸 兩個階段 地址周期(AP),只有一個cycle 數據周期(DP),由HREADY信號決定需要幾個cycle 流水線傳送 先是地址周期,然后是數據周期 AHB突發傳輸與AXI突發傳輸的特點 AHB協議需要一次突發傳輸的所有地址,地址與數據鎖定對應關系,后一次突發傳輸必須在前次傳輸完成才能進行。 AXI只需要一次突發的首地址,可以連續發送多個突發傳輸首地址而無需等待前次突發傳輸完成,并且多個數據可以交錯傳遞,此特征大大提高了總線的利用率。 AHB總線與AXI總線均適用于高性能、高帶寬的SoC系統,但AXI具有更好的靈活性,而且能夠讀寫通道并行發送,互不影響;更重要的是,AXI總線支持亂序傳輸,能夠有效地利用總線的帶寬,平衡內部系統。因此SoC系統中,均以AXI總線為主總線,通過橋連接AHB總線與APB總線,這樣能夠增加SoC系統的靈活性,更加合理地把不同特征IP分配到總線上。

1.1.4APB總線

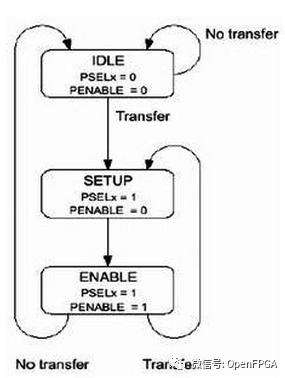

主要應用在低帶寬的外設上,如UART、 I2C,它的架構不像AHB總線是多主設備的架構,APB總線的唯一主設備是APB橋(與AXI或APB相連),因此不需要仲裁一些Request/grant信號。APB的協議也十分簡單,甚至不是流水的操作,固定兩個時鐘周期完成一次讀或寫的操作。其特性包括:兩個時鐘周期傳輸,無需等待周期和回應信號,控制邏輯簡單,只有四個控制信號。APB上的傳輸可用如圖所示的狀態圖來說明。 1、系統初始化為IDLE狀態,此時沒有傳輸操作,也沒有選中任何從模塊。 2、當有傳輸要進行時,PSELx=1,,PENABLE=0,系統進入SETUP狀態,并只會在SETUP狀態停留一個周期。當PCLK的下一個上升沿到來時,系統進入ENABLE狀態。 3、系統進入ENABLE狀態時,維持之前在SETUP狀態的PADDR、PSEL、PWRITE不變,并將PENABLE置為1。傳輸也只會在ENABLE狀態維持一個周期,在經過SETUP與ENABLE狀態之后就已完成。之后如果沒有傳輸要進行,就進入IDLE狀態等待;如果有連續的傳輸,則進入SETUP狀態。