眾所周知,setup和hold作為timing分析與驗證中最重要的概念之一,是時序電路正常工作必須滿足的條件。

但是很多初學者甚至某些工作數年的工程師,對時序電路需要驗證setup和hold背后的原理可能并不清楚。

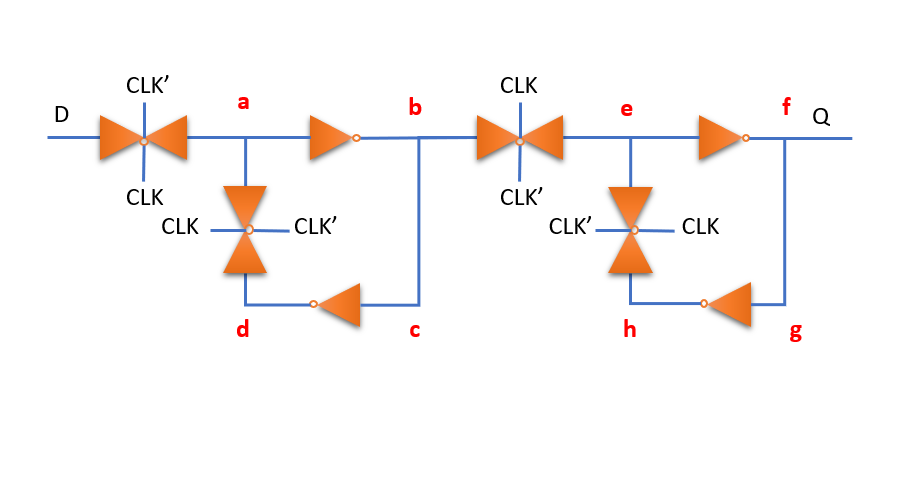

下圖是上升沿觸發的D觸發器的一種典型的基于傳輸門的設計原理:

首先我們先把注意力集中在電路的前半部分。

假設CLK的初始狀態為0,此時第一個傳輸門導通,信號走向為:

D -> a -> b -> c -> d 注:路徑1

從以上信號走向可以看出,信號必須在CLK上升沿到來之前在d點保持穩定,否則如果在這之前D pin的信號發生變化,就會導致DFF鎖住錯誤的信號。換句話說,如果假設路徑1需要花費的時間為t0,那么D處的信號必須要在CLK上升沿之前的t0或更早的時間內保持穩定。此即setup的物理意義,也是timing report種library setup time所代表的含義。

接著,當CLK從0變成1后,D與a之間的傳輸門關閉,a與d之間的傳輸門導通,此時信號走向為:

d -> a -> -> b -> e -> f(Q) -> g -> h

需要注意的是,當信號從0變為1的過程中,在一段很短的時間內,所有傳輸門都可能導通,若此時D端信號發生變化而CLK的transition比較慢,則會發生新值覆蓋舊值而導致信號錯誤的現象。因此,D段信號需要在傳輸門完成開/關過程中保持穩定,此即為hold的物理意義,也是timing report中library hold time代表的含義。