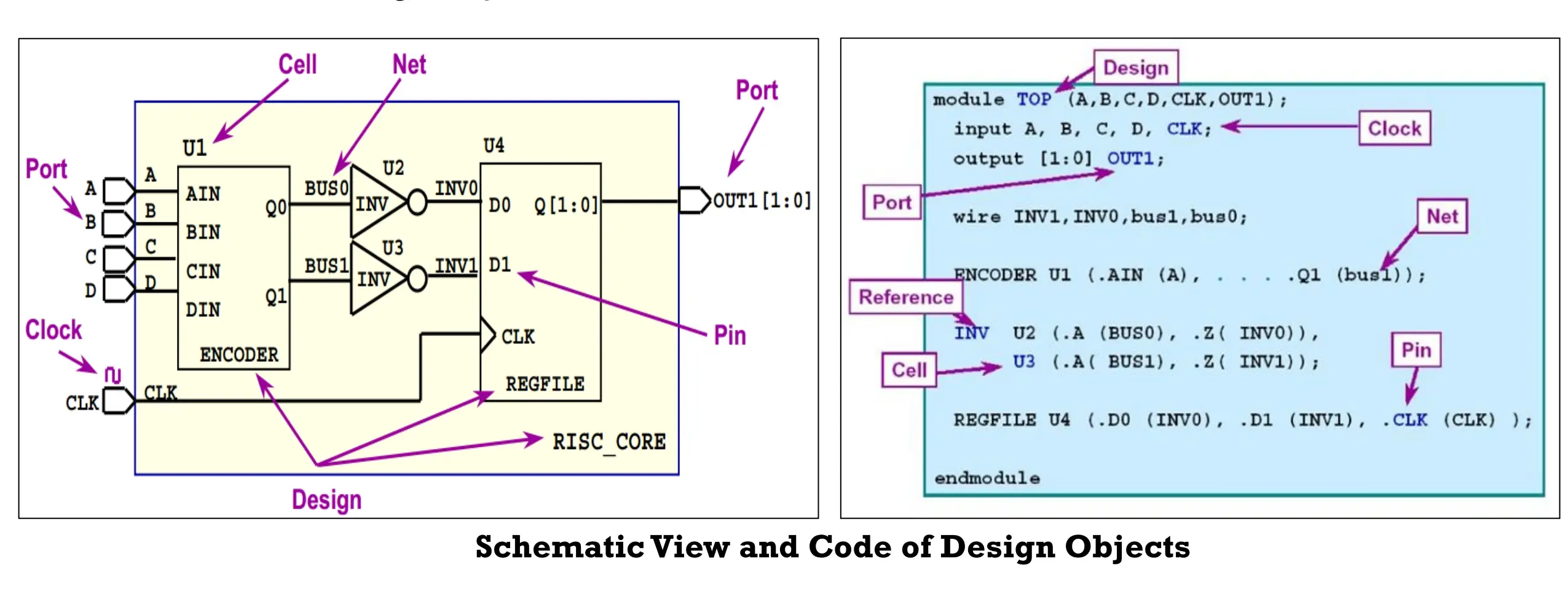

(1) Cells :器件中的基本結構單元( 例如,查找表、寄存器、IO 單元、PLL 、存儲器塊等) 。

(2) Pins:Cell 的輸入輸出端口。注意:這里的Pins 不包括器件的輸入輸出引腳。

(3) Nets:同一個Cell 中,從輸入pin 到輸出pin 經過的邏輯。注意,網表中連接兩個相鄰Cell 的連線不被看作Net,而被看作同一個點,等價于Cell 的pin 。雖然連接兩個相鄰Cell 的連線不被看作Net,但這個連線還是有其物理意義的,即等價于FPGA 器件中的一段布線邏輯,會引入一定的延遲。

(4) Ports :頂層邏輯的輸入輸出端口。對應已經分配的器件引腳