https://zhuanlan.zhihu.com/p/142377567

**關鍵詞:同步釋放,recovery,removal**

在數字IC設計中肯定會涉及到異步復位的問題,因為需要對電路進行復位操作。這種復位設計主要依靠前端設計以及工具來檢查,從數字IC后端的角度上講,只要在timing signoff階段檢查好removal和recovery的check就好。

**Removal timing check**

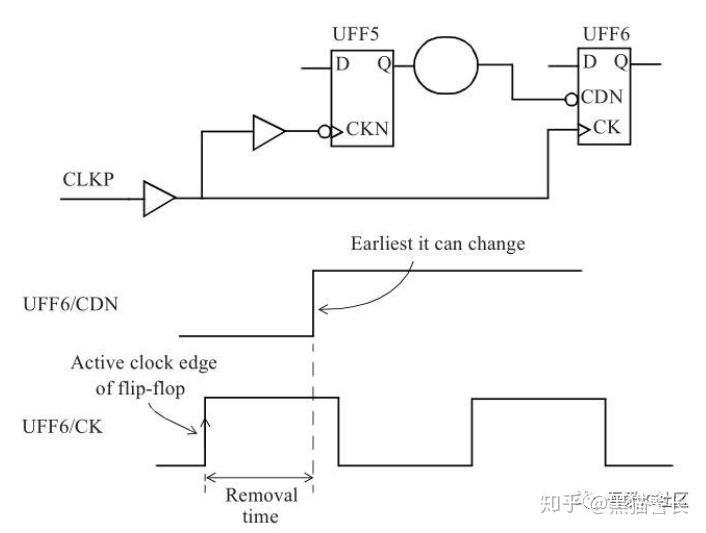

Removal time是指在時鐘有效沿來臨之后,異步復位信號需要繼續保持有效的最短時間。滿足這個最短時間才能確保對寄存器進行正常的復位。Removal time check的波形圖如下圖所示。Removal timing check與hold time check類似。

**Recovery timing check**

Recovery time是指在時鐘有效沿到來之前,復位信號保持高電平的最短時間。即復位信號變到非復位狀態的電平必須在clk之前一定的時間到達。滿足這個Recovery time,可以確保在時鐘有效沿來臨時,異步復位信號處于無效狀態,從而確保正常的數據采樣。

從Removal 和Recovery time的定義知道,只要DFF的復位信號不在時鐘有效沿附近變化(復位信號遠離時鐘有效沿),就可以保證電路的正常復位和撤銷。

在實際的設計中,比如有的模塊是先復位再給模塊供應時鐘,即保證了復位信號與時鐘在時間上是錯開的,這種流程可以保證不會出現recovery和removal的問題,因為復位置起撤銷時都沒有時鐘。即使操作流程保證不了,出現recovery和removal違例,由于模塊此時都不會工作,也沒什么問題。

**同步復位**

復位信號可以理解為一個普通的數據信號,它只有在時鐘的跳變沿才會其作用,一般只要復位信號持續時間大于一個時鐘周期,就可以保證正確復位。

**異步復位**

復位可以在任何時候發生,表面上看跟時鐘沒有關系,但真實情況是異步復位也需考慮時鐘跳變沿,因為時鐘沿變化和異步復位都可以引起Q端數據變化。如果異步復位信號跟時鐘在一定時間間隔內發生變化,Q值將無法確定,即亞穩態現象。這個時候既是異步復位信號持續時間再長都沒有辦法,因為不定態已經傳遞下去。

同步復位雖然解決了當時鐘的有效沿來臨的時候rst\_n的邊沿也正好來臨所出現的冒險與競爭。但是從綜合的電路上可以看出,多了一個組合邏輯MUX。

如果設計中所有的復位都是這樣的,那會增加很多的資源,導致芯片面積很大。那么有沒有更好的解決辦法呢?答案是有,那就是**異步復位同步釋放機制。**

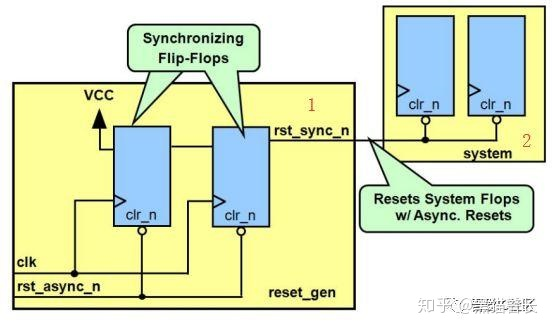

**異步復位,同步釋放**

異步復位,同步釋放就是指在復位信號到來的時候不受時鐘信號的同步,而是在復位信號釋放的時候受到時鐘信號的同步。

- 空白目錄

- 流水線

- 流水線性能測評

- 計算機性能測評

- 流水線設計

- 購物車狀態機

- 序列檢測器

- 序列檢測10010

- 序列檢測10010帶圖

- 反相器

- 計數器

- 分頻電路

- 偶數分頻

- 奇數分頻

- 小數分頻

- 同步復位異步釋放all

- 對的-異步復位同步釋放原理

- 同步復位異步釋放

- 異步復位為什么要同步釋放 ?

- FPGA-異步復位同步釋放 通俗解釋

- 同步復位

- 狀態機

- 狀態機的分類

- 狀態機5個要素

- FIFO

- 異步fifo中同步為什么要用兩級觸發器

- 亞穩態

- 亞穩態的產生機理、消除辦法 (可以理解為什么打拍)

- 面向對象思想

- 為什么D觸發器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自啟動

- 毛刺

- 馮諾依曼