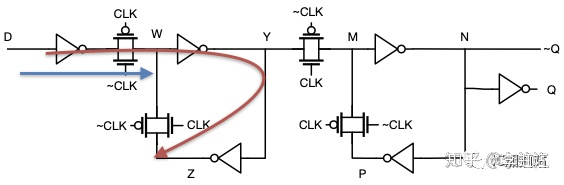

它們與D觸發器的內部結構有關系。D觸發器的內部是一個主從鎖存器(master-slave latch),一個常見的D觸發器結構如下圖所示

Latch能夠存儲住狀態,靠的是上面的背靠背的反相器。而這個背靠背的反相器能夠鎖住狀態是需要時間的。由此,我們可以分析出

setup time: 在clk的上升沿到來之前,D要傳輸到Z的時間。因為當Z的值還沒有穩定的時候,D如果變化,那么這個背靠背的反相器就無法鎖住值。

hold time: 第一個傳輸門關閉需要的時間,在傳輸門關閉期間,D->W要保持穩定,這樣在傳輸門關閉之后,W穩定才不會導致背靠背反相器鎖住的值發生變化。

所以我們可以看出,當D在setup/hold time window內發生變化,鎖存器可能無法鎖住一個穩定的值,會發生的結果是

* Q的值可能不是正確的D

* 隨著D的變化越靠近時鐘沿,Q變穩定的時間越長

* 最后Q穩定到的值可能是隨機的

注意我們并不是說Q最后的值不是穩定的1或者0, Q的值最后一定會穩定下來,穩定在高電平或者低電平,這是由于背靠背的反相器會產生正反饋,最終一定會穩定下來。但是當這個穩定的時間超出了clk-to-q的限制,我們就說產生了亞穩態。

- 空白目錄

- 流水線

- 流水線性能測評

- 計算機性能測評

- 流水線設計

- 購物車狀態機

- 序列檢測器

- 序列檢測10010

- 序列檢測10010帶圖

- 反相器

- 計數器

- 分頻電路

- 偶數分頻

- 奇數分頻

- 小數分頻

- 同步復位異步釋放all

- 對的-異步復位同步釋放原理

- 同步復位異步釋放

- 異步復位為什么要同步釋放 ?

- FPGA-異步復位同步釋放 通俗解釋

- 同步復位

- 狀態機

- 狀態機的分類

- 狀態機5個要素

- FIFO

- 異步fifo中同步為什么要用兩級觸發器

- 亞穩態

- 亞穩態的產生機理、消除辦法 (可以理解為什么打拍)

- 面向對象思想

- 為什么D觸發器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自啟動

- 毛刺

- 馮諾依曼