# 1\. 應用背景

## 1.1???????? 亞穩態發生原因

????? 在[FPGA]系統中,如果數據傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位信號的釋放相對于有效時鐘沿的恢復時間(recovery time)不滿足,就可能產生亞穩態,此時觸發器輸出端Q在有效時鐘沿之后比較長的一段時間處于不確定的狀態,在這段時間里Q端在0和1之間處于振蕩狀態,而不是等于數據輸入端D的值。這段時間稱為決斷時間(resolution time)。經過resolution time之后Q端將穩定到0或1上,但是穩定到0或者1,是隨機的,與輸入沒有必然的關系。

## 1.2???????? 亞穩態發生場合

????? 只要系統中有異步元件,亞穩態就是無法避免的,亞穩態主要發生在異步信號檢測、跨時鐘域信號傳輸以及復位電路等常用設計中。

## 1.3???????? 亞穩態危害

????? 由于產生亞穩態后,寄存器Q端輸出在穩定下來之前可能是毛刺、振蕩、固定的某一電壓值。在信號傳輸中產生亞穩態就會導致與其相連其他數字部件將其作出不同的判斷,有的判斷到“1”有的判斷到“0”,有的也進入了亞穩態,數字部件就會邏輯混亂。在復位電路中產生亞穩態可能會導致復位失敗。怎么降低亞穩態發生的概率成了FPGA設計需要重視的一個注意事項。

# 2. 理論分析

## 2.1???? 信號傳輸中的亞穩態

???? 在同步系統中,輸入信號總是系統時鐘同步,能夠達到寄存器的時序要求,所以亞穩態不會發生。**亞穩態問題通常發生在一些跨時鐘域信號傳輸以及異步信號采集上。**

它們發生的原因如下:

(1)在跨時鐘域信號傳輸時,**由于源寄存器時鐘和目的寄存器時鐘相移未知**,所以源寄存器數據發出數據,數據可能在任何時間到達異步時鐘域的目的寄存器,所以無法保證滿足目的寄存器Tsu和Th的要求;

(2)在異步信號采集中,由于異步信號可以在任意時間點到達目的寄存器,所以也無法保證滿足目的寄存器Tsu和Th的要求;

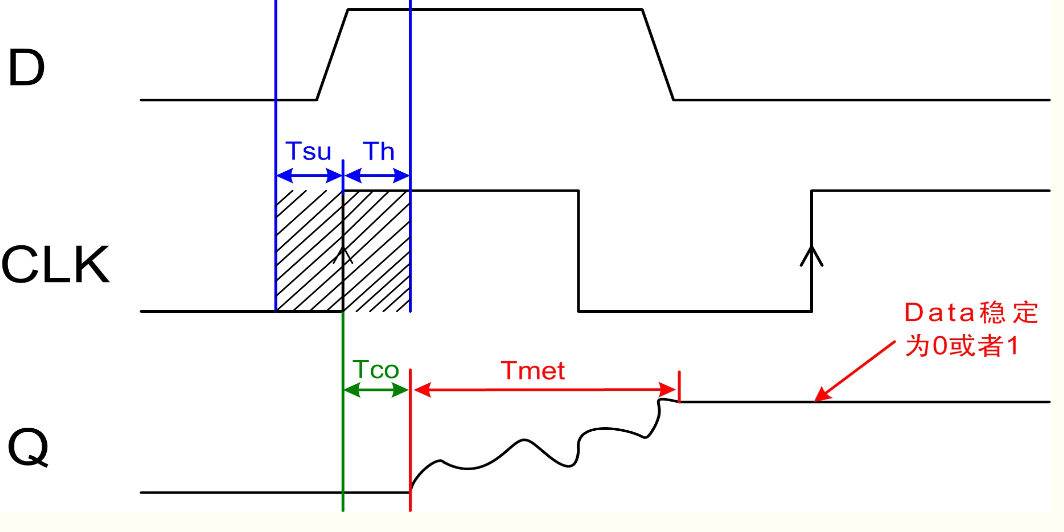

當數據在目的寄存器Tsu-Th時間窗口發生變化,也即當數據的建立時間或者保持時間不滿足時,就可能發生亞穩態現象。如圖2.1所示。

由圖可知,當產生亞穩態后Tco時間后會有Tmet(決斷時間)的振蕩時間段,當振蕩結束回到穩定狀態時為“0”或者“1”,這個是隨機的。因此,會對后續電路判斷造成影響。

## 2.2???????? 復位電路的亞穩態

### 2.2.1??? 異步復位電路

在復位電路設計中,復位信號基本都是異步的,常用異步復位電路Verilog描述如下:

```

always @(posedge clk or negedge rst\_n)

begin

?????? if(!rst\_n) a <= 1’b0;

?????? else???????? a <= b;

end

```

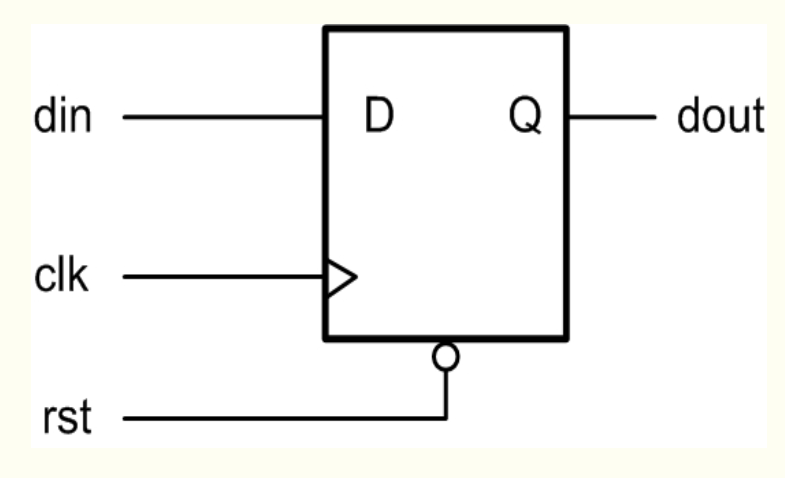

綜合出來復位電路模型如圖2.2所示:

? ? ?圖 2.2? 異步復位電路模型

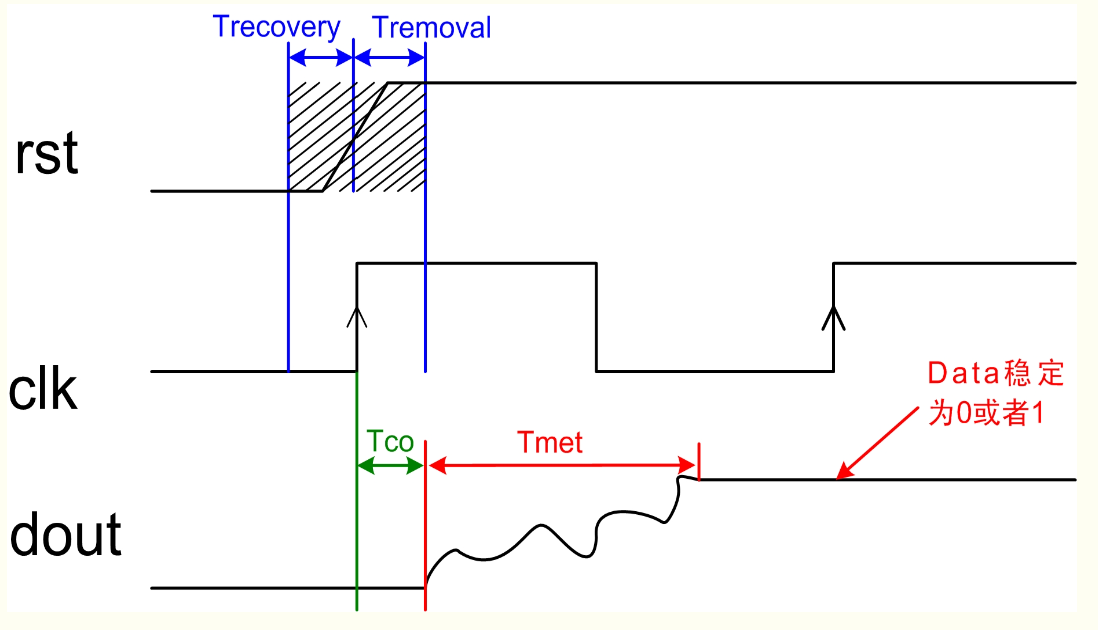

如圖2.3所示,為復位電路復位時序圖。如果異步復位信號的撤銷時間在Trecovery(恢復時間)和Tremoval(移除時間)之內,那勢必造成亞穩態的產生,輸出在時鐘邊沿的Tco后會產生振蕩,振蕩時間為Tmet(決斷時間),最終穩定到“0”或者“1”,就會可能造成復位失敗。

圖2.3? 異步復位時序

## 2.2.1.1 恢復和去除時間(Recovery and Removal Time)

恢復時間(Recovery Time)是指異步控制信號(如寄存器的異步清除和置位控制信號)在“下個時鐘沿”來臨之前變無效的最小時間長度。這個時間的意義是,如果保證不了這個最小恢復時間,也就是說這個異步控制信號的解除與“下個時鐘沿”離得太近(但在這個時鐘沿之前),**沒有給寄存器留有足夠時間來恢復至正常狀態,那么就不能保證“下個時鐘沿”能正常作用,也就是說這個“時鐘沿”可能會失效。**

去除時間(Removal)是指異步控制信號(如寄存器的異步清除和置位控制信號)在“有效時鐘沿”之后變無效的最小時間長度。這個時間的意義是,如果保證不了這個去除時間,也就是說這個**異步控制信號的解除與“有效時鐘沿”離得太近(但在這個時鐘沿之后),那么就不能保證有效地屏蔽這個“時鐘沿”,也就是說這個“時鐘沿”可能會起作用。**

- 空白目錄

- 流水線

- 流水線性能測評

- 計算機性能測評

- 流水線設計

- 購物車狀態機

- 序列檢測器

- 序列檢測10010

- 序列檢測10010帶圖

- 反相器

- 計數器

- 分頻電路

- 偶數分頻

- 奇數分頻

- 小數分頻

- 同步復位異步釋放all

- 對的-異步復位同步釋放原理

- 同步復位異步釋放

- 異步復位為什么要同步釋放 ?

- FPGA-異步復位同步釋放 通俗解釋

- 同步復位

- 狀態機

- 狀態機的分類

- 狀態機5個要素

- FIFO

- 異步fifo中同步為什么要用兩級觸發器

- 亞穩態

- 亞穩態的產生機理、消除辦法 (可以理解為什么打拍)

- 面向對象思想

- 為什么D觸發器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自啟動

- 毛刺

- 馮諾依曼