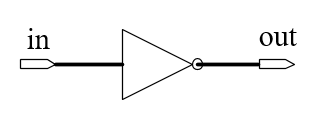

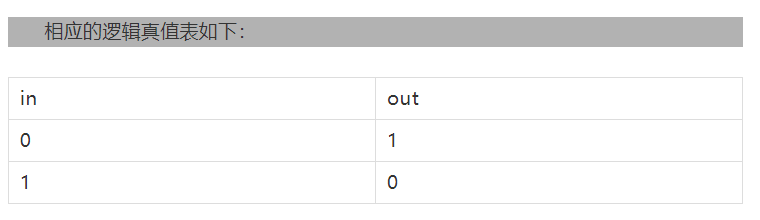

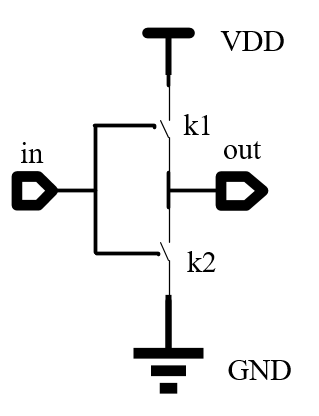

非門實現的是邏輯功能為? out = -in, 即將輸入信號做一個反向,故也稱為反相器。其門級示意圖如下:

Verilog描述如下(“//”后面的語句為注釋語句):

```

? ? wire? in;? ? ? ? ? ? ? ? ? ?//wire 為線信號關鍵字

? ? wire? out;

? ? assign? ?out = ~in;? //assign 為賦值語句,~表示反向;

```

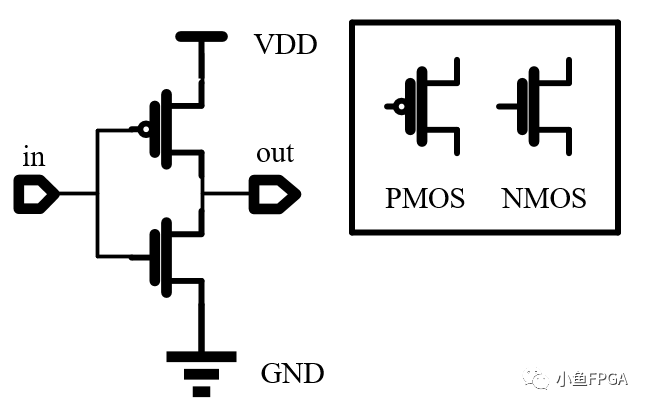

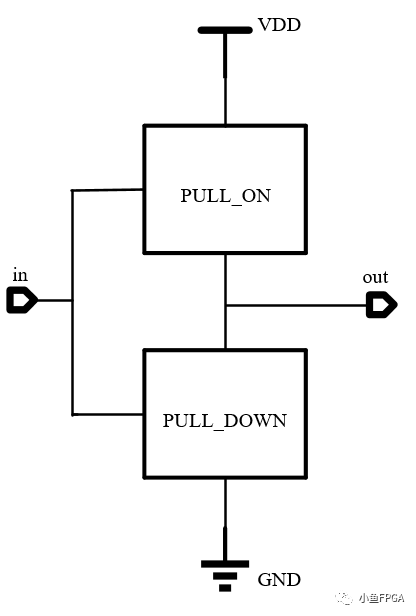

相應的CMOS結構如下:由一個PMOS和NMOS組成,PMOS做上拉,與VDD相連;NMOS做下拉,與GND相連。

簡單分析一下我們要實現的功能,無非就是當 in 為 0 (低電平)時,out輸出為1(高電平),即out跟電源VDD相連;當 in 為 1(高電平)時,out輸出為0(低電平),即out要跟GND(地)相連。故上面的非門CMOS電路的等效電路如下:當in 為0時開關k1閉合,k2打開,即out與VDD相連,輸出為1;當in 為1時開關k1打開,k2閉合,即out與GND相連,輸出為0。

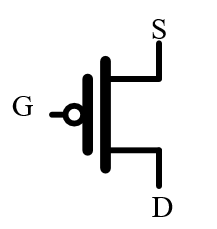

? ? ?故PMOS相當于一個開關,如下當G端為低電平時,D端與S端才連通;

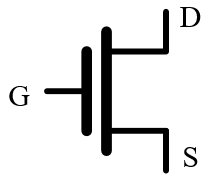

? ? ?故NMOS相當于一個開關,如下當G端為高電平時,D端與S端才連通;

拓展:現在常見的數字集成電路其底層的基本邏輯電路都是由CMOS結構構成。上拉邏輯部分由PMOS組成,下拉邏輯部分由NMOS組成。反相器就是一個最基本的CMOS邏輯電路,上拉部分只有一個PMOS,下拉部分只有一個NMOS。后面還會講到其它邏輯門電路,到時候大家對CMOS邏輯的了解就更深入了。

- 空白目錄

- 流水線

- 流水線性能測評

- 計算機性能測評

- 流水線設計

- 購物車狀態機

- 序列檢測器

- 序列檢測10010

- 序列檢測10010帶圖

- 反相器

- 計數器

- 分頻電路

- 偶數分頻

- 奇數分頻

- 小數分頻

- 同步復位異步釋放all

- 對的-異步復位同步釋放原理

- 同步復位異步釋放

- 異步復位為什么要同步釋放 ?

- FPGA-異步復位同步釋放 通俗解釋

- 同步復位

- 狀態機

- 狀態機的分類

- 狀態機5個要素

- FIFO

- 異步fifo中同步為什么要用兩級觸發器

- 亞穩態

- 亞穩態的產生機理、消除辦法 (可以理解為什么打拍)

- 面向對象思想

- 為什么D觸發器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自啟動

- 毛刺

- 馮諾依曼