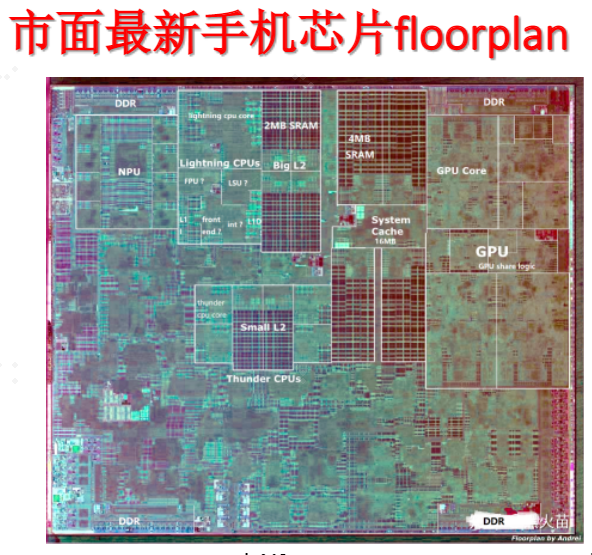

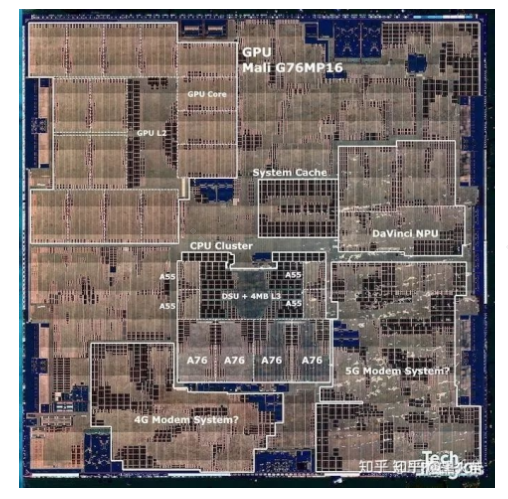

Floorplan的目的是為了確定模塊大小,位置,形狀,以及擺放Macro,也就是我們通常見到的隨機存儲單元RAM、只讀存儲單元ROM,還有其他IP模塊等等。它與Place(布局)有著一些相似的地方。Floorplan的復雜之處在于模塊的形狀與大小可能是一個不確定的變量,需要權衡結果來反推這個變量。而其簡單之處在于,Floorplan相比于Place的超大規模標準單元而言,整體數據量并不是十分龐大。

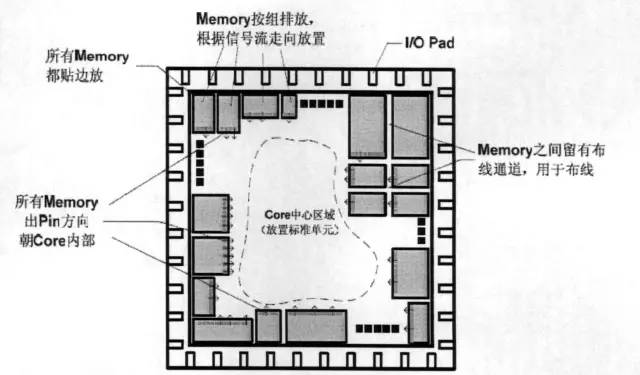

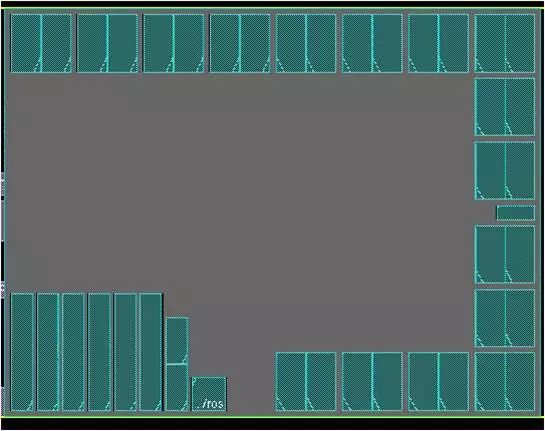

對于Floorplan而言,人們更傾向于靠自己的經驗去擺放Macro,擺放它們時不僅要考慮面積、互聯線長等傳統問題,還需要考慮Place階段,Macro的擺放對于Place的影響。因為Macro從本質上講就是一個巨型的標準單元,很多Macro也存在于各個模塊內,在Floorplan階段并不能和模塊對等的考慮。對于這個問題,人們根據實際生活中的經驗,提出一種邊緣擺放(edgeplace)的方法

因為長久以來,人們在使用具有矩形或者多邊形結構的平面石磚砌墻或者鋪地面的時候發現一個規律,要想更好的利用手頭的材料,更少的產生材料的冗余,需要先從平鋪區域的邊邊角角開始工作,并且首先將最大塊的材料鋪于區域中,再向中心擴展,并用一些小材料填補區域上的空隙。

邊緣擺放的好處主要來源于下面兩點:

a.從目前芯片設計的趨勢來看,芯片中除了計算單元,隨機存儲單元RAM、只讀存儲單元ROM等。這些存儲單元占據的芯片面積在有些設計中甚至超過百分之五十。對于存儲單元來說,存在數據端口和存儲端口,并且周圍需要有一些可測性[電路]。這使得這些單元引線眾多且功耗巨大。將它們貼邊放置,不僅有利于這些單元的供電,而且防止這些單元過多的引腳對其他單元的布線造成影響。

b.標準單元在布局時,按照Row所劃定的高度一排一排的擺放,這樣既有利于算法的設計,又有利于工業制造。并且在給各個器件供電時,可以使用橫向的電源線將處于同一高度的器件連接在一起統一供電。若是將標準單元都擺放在芯片區域的中心,而大的Macro擺放在四周,就可以使標準單元方便的只用一條電源線連接在一起,而不會被高度不統一的Macro打斷。對電源網格的設計提供了巨大便利。

b.大的Macro擺放盡量貼近版圖的邊緣和角落,這樣有利用空間的利用。如下圖所示

c.Macro與Macro之間要留有一定空隙,給予布線資源。特別是在Macro的間隙有端口的時候更是如此,設計者可以通過相鄰Marco邊界上端口的多少來決定留有多大的間隙比較合適。在使用[EDA](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)軟件的Floorplan設計時,同樣可以給Macro加上halo來控制Macro與Macro之間的距離。Halo分為placementhalo和rou[ti](http://www.elecfans.com/tags/ti/)nghalo,可以分別阻止在有Halo區域放置其他單元或者繞線,類似于blockage。但是Halo并不是獨立存在,而是依附于Macro周圍,可隨Macro移動的。所以它是專門用來控制Macro和其他單元之間距離的一種功能。

- 電子元器件

- 電阻

- 電容器

- 電感

- 保險絲

- 二極管

- 三極管

- 接插件

- 蜂鳴器

- MOS

- 集成電器基礎知識

- 接地的基礎知識

- STA

- Skew

- setup和hold

- 問題

- timing path

- Latency

- 跨時鐘域的代碼檢查(spyglass)

- 時間換算

- 名詞解釋

- 寄存器

- 觸發器

- ECO

- 通用芯片和嵌入式芯片有什么區別

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 邏輯閾值

- Floorplan

- 寄存器傳輸的設計(RTL)

- 集成電路設計方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片設計

- 什么是Scenario?

- 晶圓BUMP加工工藝和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency與delay區別

- Power

- LVT, RVT, HVT 的區別

- PPA

- RTL

- 芯片行業的IP是指什么?

- 晶振與晶體的區別

- PLL (鎖相環(PhaseLockedLoop))

- 奇偶分頻電路

- inverter

- glitch (電子脈沖)

- Power

- Clock Gating

- 低功耗設計

- UPF

- 低功耗單元庫

- Power intent

- 亞穩態

- 芯片流程

- 芯片軟件

- 亞穩態&MTBF&同步器&AFIFO

- glitch free的時鐘切換技術

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生電路?

- 晶振

- 信號完整性

- 什么是脈沖?什么是電平?

- 閾值電壓

- bump

- IC設計常用文件及格式介紹

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI簡介

- 異步橋

- 芯片后仿之SDF

- 慕課-VLSI設計基礎(數字集成電路設計基礎)

- 概論

- MOS晶體管原理

- 設計與工藝接口

- 反相器和組合邏輯電路

- 問題trainning