上面列舉了芯片設計領域比較常見的低功耗設計方向,其中應用最多的就是優化芯片架構,升級生產工藝、降低芯片工作電壓、采用不同速度的標準單元,分區域采用不同電壓的電源以及模塊關斷(多電壓域),而其中和后端設計有關的,基本上有以下幾種:

**升級生產工藝;**

**降低芯片工作電壓;**

**關斷部分時鐘(Clock Gating);**

**采用不同速度的標準單元(Multi-Vth庫);**

**多電壓域設計(Multi-Voltage)。**

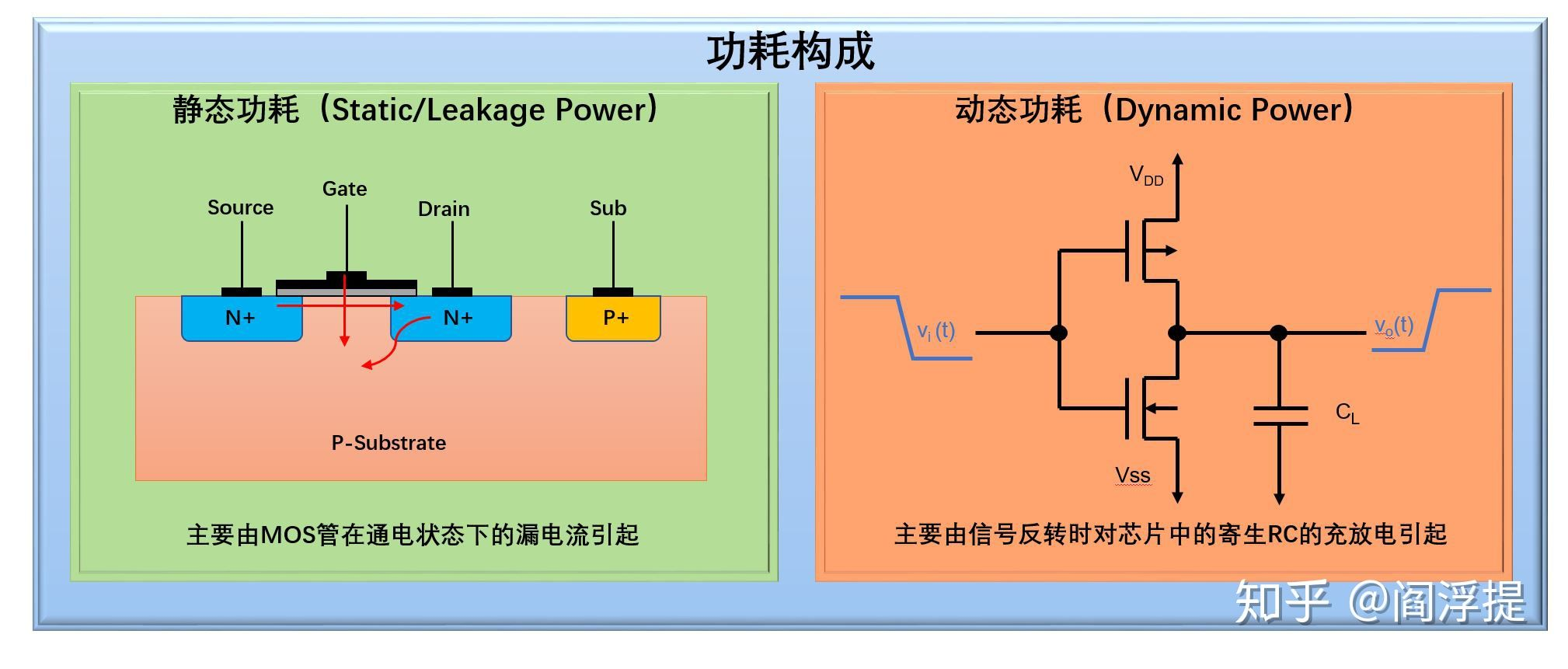

在詳細解釋上述概念之前,我想先把芯片中主要的功耗構成簡單提一下。芯片功耗主要分為靜態功耗和動態功耗,基本原理如下圖所示:

* **升級工藝**

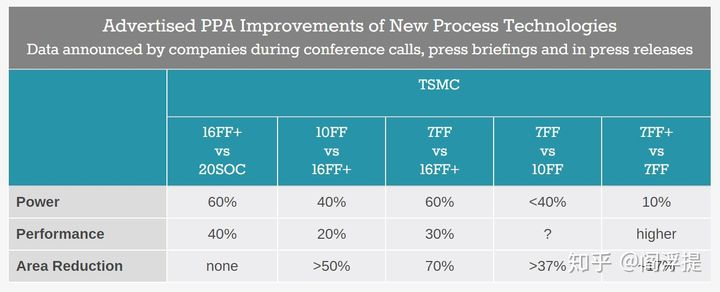

這是應用最廣泛,最行之有效的方法之一。它的原理在于,隨著晶體管的尺寸越來越小,leakage power在芯片整體功耗中所占的比重越來越大,而先進工藝的晶體管尺寸更小,泄漏電流也更小,從而能夠整體降低leakage power。因此我們經常能夠看到這樣的新聞:某某芯片從22nm升級到14nm,性能提升x%,功耗降低y%等。這其中的功耗降低固然可能包含架構方面的改善,但是工藝升級帶來的優勢一定是非常明顯的。

* **降低芯片工作電壓**

按照中學物理的計算公式,功率與電壓和電流的乘積正相關。在芯片上計算功耗雖然沒有這么簡單,但是從原理上降低芯片電壓仍然是降低功耗最直觀最有效的方法。也正因為如此,當前大多數芯片的工作電壓從最初的5V、3V一路下降,目前基本都在1V以下甚至0.5V以下。而隨之而來的困難在于,隨著電壓的下降,標準單元的速度也會隨之變慢,但是電子設備對處理速度亦即芯片頻率的要求卻越來越高。以移動設備為例,最初的芯片頻率不過幾十上百兆赫茲,而現今最快的手機SoC頻率峰值已經超過2GHz。這方面也是每一代芯片升級背后所需要解決的技術難題之一。

* **關斷時鐘(Clock Gating)**

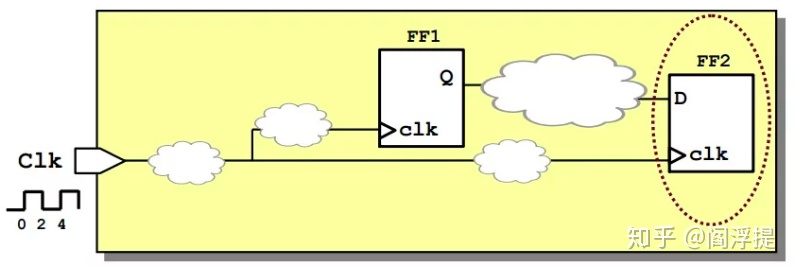

動態功耗主要是由信號的翻轉引起的,而在芯片中,翻轉最頻繁的信號就是時鐘(Clock)信號。我們知道,芯片中各種邏輯功能的傳輸,數據保存等電路是由下列timing path組成的:

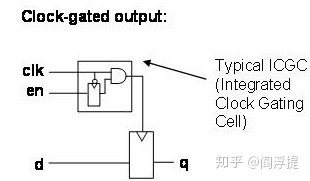

簡而言之,就是前面的FF1寄存器的數據通過一系列運算后,在時鐘信號clk的作用下,被后面的FF2寄存器捕捉,完成一次數據傳輸。但在實際中會有這樣的情況發生:FF1傳過來的數據和FF2當前保存的數據相同,也就是FF2的數據無需翻轉刷新仍能保證功能的正確性,而此時clk仍然翻轉一次刷新了FF2的數據。這種情況盡管在功能上沒有任何問題,但是在功耗方面卻是實實在在的浪費。因此,在電路設計階段以及邏輯綜合階段,設計者和EDA工具會根據芯片的功能和實際數據的變化情況,人為或者自動地插入一系列的clock gating cell,從而保證僅在數據發生變化的時候信號才會翻轉。下面是典型的Integrated Clock Gating(ICG)的結構:

* **采用不同速度的標準單元(Multi-Vth庫)**

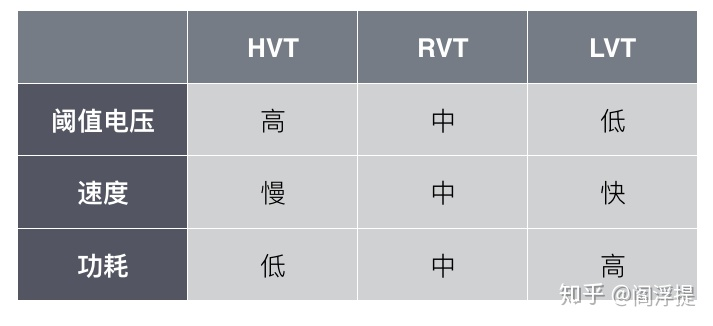

這是當前芯片行業最常用也是最容易使用的設計方法之一。所謂Vth,指的是邏輯門的閾值電壓。而閾值電壓和功耗與速度存在如下關系:閾值電壓越高,cell速度越慢,功耗越小;反之閾值電壓越低,cell速度越快,功耗越高。

在實際應用中,一般采用的策略為:對于性能要求高的模塊,或者頻率比較高的部分,采用Vth比較低的cell,讓setup更容易收斂;對于性能要求較低的模塊,或者頻率較低的部分,多采用Vth比較高的cell,讓功耗更低。通過這種方法,可以實現在同一塊芯片上,根據性能和功耗的不同要求而調整cell的使用,從而避免在不太重要的功能上浪費過多的功耗。

* **多電壓域設計(Multi-Voltage, Power Gating)**

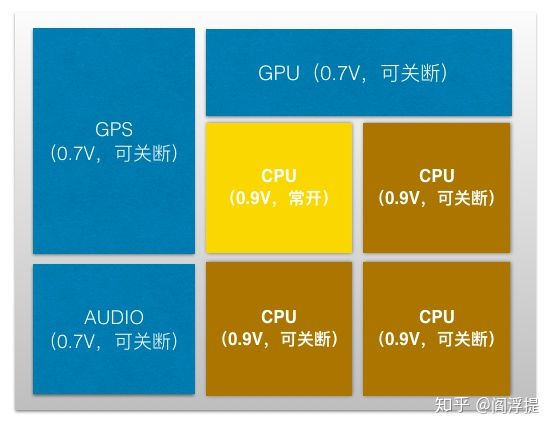

在使用手機的時候,我們經常會遇到這種情況:當我們看到電池快要沒電而手頭有沒有充電設備的時候,我們會盡量關閉所有應用,不再聽歌不再看視頻,甚至連地圖的定位與導航功能都不再開啟,其根本目的就在于減少消耗電池的功能。在芯片設計中也引入了這種理念:一顆SoC中可能包含很多功能模塊如視頻處理(DSP),音頻處理(AUDIO),定位(GPS),游戲(GPU),存儲(Memory)等,但大多數功能并不會同時開啟,因此為了降低不用模塊在等待狀態下消耗的功耗,干脆就設計成在不用的時候把它們關閉。這就是Power Gating最初的想法。與此同時,對于性能要求較高的CPU,GPU等模塊,由于需求頻率較高,在設計上可能采用較高的電壓,而一些不太核心的模塊如AUDIO,GPS等,可以采用相對低的電壓來設計。這樣一來,整顆芯片可能就會變成下面的樣子(下圖不影射任何實際芯片):

這樣一來,芯片的功耗最低時僅有一個CPU內核處于開啟狀態,可以大幅度減少其他模塊在等待時的電量消耗,從而增加電池使用時間。

盡管它的思路很簡單,但是在實際設計中不管是不同電壓還是模塊關斷,都會帶來很多額外的問題,這些問題以及業界普遍應用的解決方案我們將在后面的文章中一一提及

- 電子元器件

- 電阻

- 電容器

- 電感

- 保險絲

- 二極管

- 三極管

- 接插件

- 蜂鳴器

- MOS

- 集成電器基礎知識

- 接地的基礎知識

- STA

- Skew

- setup和hold

- 問題

- timing path

- Latency

- 跨時鐘域的代碼檢查(spyglass)

- 時間換算

- 名詞解釋

- 寄存器

- 觸發器

- ECO

- 通用芯片和嵌入式芯片有什么區別

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 邏輯閾值

- Floorplan

- 寄存器傳輸的設計(RTL)

- 集成電路設計方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片設計

- 什么是Scenario?

- 晶圓BUMP加工工藝和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency與delay區別

- Power

- LVT, RVT, HVT 的區別

- PPA

- RTL

- 芯片行業的IP是指什么?

- 晶振與晶體的區別

- PLL (鎖相環(PhaseLockedLoop))

- 奇偶分頻電路

- inverter

- glitch (電子脈沖)

- Power

- Clock Gating

- 低功耗設計

- UPF

- 低功耗單元庫

- Power intent

- 亞穩態

- 芯片流程

- 芯片軟件

- 亞穩態&MTBF&同步器&AFIFO

- glitch free的時鐘切換技術

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生電路?

- 晶振

- 信號完整性

- 什么是脈沖?什么是電平?

- 閾值電壓

- bump

- IC設計常用文件及格式介紹

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI簡介

- 異步橋

- 芯片后仿之SDF

- 慕課-VLSI設計基礎(數字集成電路設計基礎)

- 概論

- MOS晶體管原理

- 設計與工藝接口

- 反相器和組合邏輯電路

- 問題trainning