PTPX在功耗分析中的作用

當今,隨著工藝的越來越深入,芯片的漏電也變得越來越大。而且芯片的性能也越來越高,如之前的matrix只要幾十Mhz,現在都需要上百Mhz這樣的頻率。而且CPU/GPU的主頻也變得越來越高。又由于現在人們越來越講究電池的續航能力,無論是手持設備,還是筆記本,人們都希望自己的電子設備待機時間越長越好。所以,種種原因,降低功耗提高到了一個空前的關注度。

那么,本文就相關PTPX在功耗分析中的作用,稍微簡述一下。

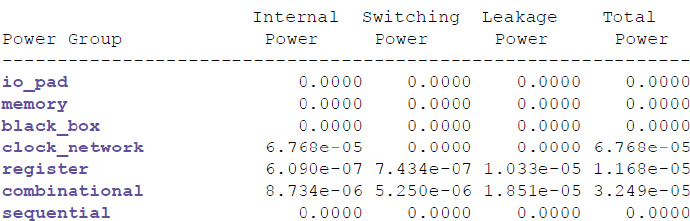

首先,功耗大致包括total power = leakage power +internal power?+ switching power。其中internal power + switch power = dynamic power.

Leakage power,即漏電功耗和本身工藝庫特性相關,后端可以對non-crtical path進行cell的替換,從LVTàSVT,SVTàHVT,HVTàUHVT。另外,也可以對設計進行劃分power domain。當這個模塊不工作的時候,可以進行斷電。從而大大降低芯片的漏電功耗。

Internal?power,即短路功耗,即上下PMOS和NMOS同時導通時的功耗。當物理上cell驅動transition time很差的時候,會導致chip的internal?power有異樣。

Switch?power,即開關功耗。動態功耗和data的翻轉率(TR),靜態概率(SP),電壓,負載電容相關。一般情況下,需要讀入SPEF文件,從而抽取每個節點上的RC參數用于計算switch?power。

第二,我們可以設置以下命令可以讓PrimeTime進入功耗分析模式:

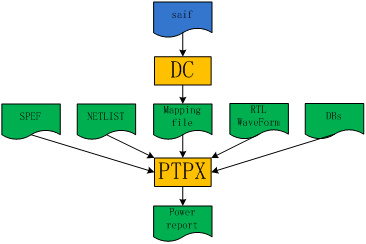

set power\_enable\_analysis true

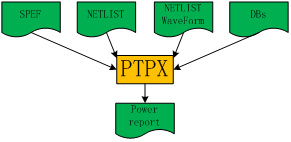

PTPX可以在設計的不同階段,可以采用不同的模式進行功耗的分析。下面提供PTPX兩種不同的流程。方式一比較適合大型設計,大型設計的后端都比較難出,所以采用RTL的waveform,通過PTPX的propagation算法,自動推導出netlist上每個節點的翻轉,即(TR,SP),進而得到功耗。另外也非常適合在設計的早期階段,評估和計算設計中的功耗。方式二,比較適合小型設計。另外加上后仿波形相對容易獲取,那么可以采用方式二獲得功耗值。方式二相比方式一在功耗值上更接近芯片回片真實值。

第三,從PTPX中我們可以獲取average power和time-based power.

從Average power中我們可以獲取clk tree power,這是我們關注的重點。經驗值告訴我們,在重負載情況下,clk tree power占據1/3total power。對于Combinational power,根據經驗,對于大型算法模塊,如通信算法,圖像處理ISP等。在RTL階段可能看不出power的異樣,一旦加入SDF就會發現power成倍增加,這是大家小心的地方。

下面是time\-based power曲線圖,可以看出整個數據發包,收包,解包過程的功耗變化趨勢。

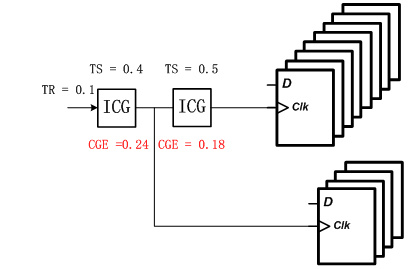

第四,PTPX不僅能夠提供功耗值,還能利用PTPX找出功耗為什么過大的原因。主要利用的特性為clock gating efficiency,clock gating ratio以及register gating efficiency。 經驗表明,提高CGE,可以高效的對功耗進行優化。下圖為一個CGE的概括圖,CGE和clock-gating cell后面帶的filp-flop的個數,以及CG cell本身的toggle?rate saving系數相關。

綜上,可以使用PTPX的average power、time-based power、clock?gating efficiency、clock gating ratio、Q/CP等feature對設計進行功耗的評估,給出功耗優化的指導方向。

- 電子元器件

- 電阻

- 電容器

- 電感

- 保險絲

- 二極管

- 三極管

- 接插件

- 蜂鳴器

- MOS

- 集成電器基礎知識

- 接地的基礎知識

- STA

- Skew

- setup和hold

- 問題

- timing path

- Latency

- 跨時鐘域的代碼檢查(spyglass)

- 時間換算

- 名詞解釋

- 寄存器

- 觸發器

- ECO

- 通用芯片和嵌入式芯片有什么區別

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 邏輯閾值

- Floorplan

- 寄存器傳輸的設計(RTL)

- 集成電路設計方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片設計

- 什么是Scenario?

- 晶圓BUMP加工工藝和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency與delay區別

- Power

- LVT, RVT, HVT 的區別

- PPA

- RTL

- 芯片行業的IP是指什么?

- 晶振與晶體的區別

- PLL (鎖相環(PhaseLockedLoop))

- 奇偶分頻電路

- inverter

- glitch (電子脈沖)

- Power

- Clock Gating

- 低功耗設計

- UPF

- 低功耗單元庫

- Power intent

- 亞穩態

- 芯片流程

- 芯片軟件

- 亞穩態&MTBF&同步器&AFIFO

- glitch free的時鐘切換技術

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生電路?

- 晶振

- 信號完整性

- 什么是脈沖?什么是電平?

- 閾值電壓

- bump

- IC設計常用文件及格式介紹

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI簡介

- 異步橋

- 芯片后仿之SDF

- 慕課-VLSI設計基礎(數字集成電路設計基礎)

- 概論

- MOS晶體管原理

- 設計與工藝接口

- 反相器和組合邏輯電路

- 問題trainning