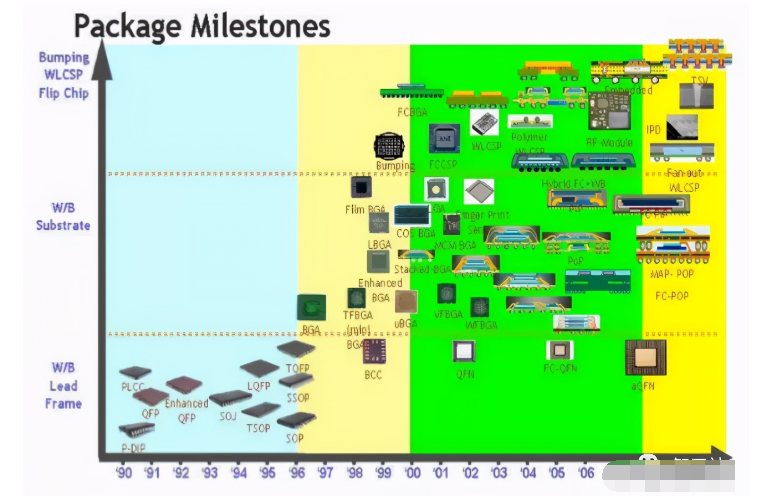

隨著現代電子裝置對小型化、輕量化、高性能化、多功能化、低功耗化和低成本化方面的要求不斷提高,IC芯片的特征尺寸不斷縮小,且集成規模迅速擴大,芯片封裝技術也在不斷革新,凸點加工工藝(Bumpprocessflow)也因此發展起來。

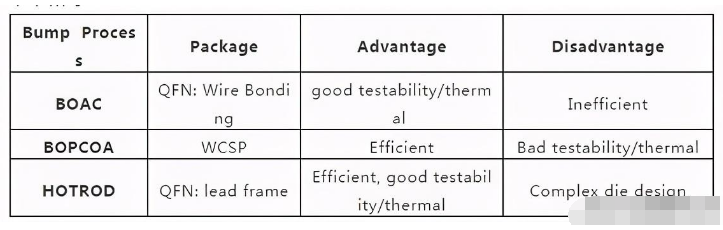

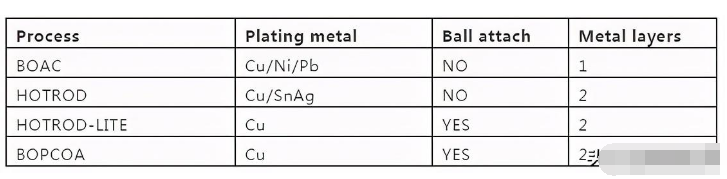

Bumpprocess分為三種:BOPCOA、BOAC、HOTROD,其封裝的優缺點如下表所示。

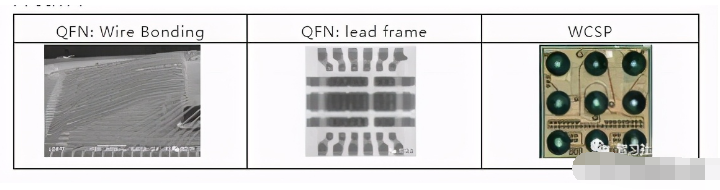

對于芯片尺寸要求沒那么嚴格的情況,大多數產品都是采用QFN封裝形式的芯片,因其可測性和散熱較好;而對于耳機、手機等小型化產品的芯片,大多采用WSCP(wafers calechippackage)封裝。同一種功能的芯片而言可以加工成不同的封裝形式,僅在Bump和Assembly層面有所區別,可以理解為QFN封裝在完成Bump制程后還需要打線(WireBonding)或者引線框架(leadframe)將引腳引出,最后塑封[成型](http://www.hqpcb.com/),而WCSP則在Bump完成Ballattach之后就是一顆完整可以交付到客戶手上的芯片了,這可以減少很多的設計開發成本。

為了更好的理解bump制程工藝,接下來簡單介紹一下WCSP的工藝流程。

Bump的制程在fab之后,fab是將電路部分加工完成,一般有三層metal,最上層留有[via](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)top,便于bump進行下一步的加工。一般從fab過來的wafer都會有一道宏觀檢測,去檢測是否從fab過來就有defect,類似[刮傷](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)、[污染](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)、破片之類的問題。然后再做清除和烘烤去除wafer上的松散顆粒和有機污染物以及wafer上的水分。

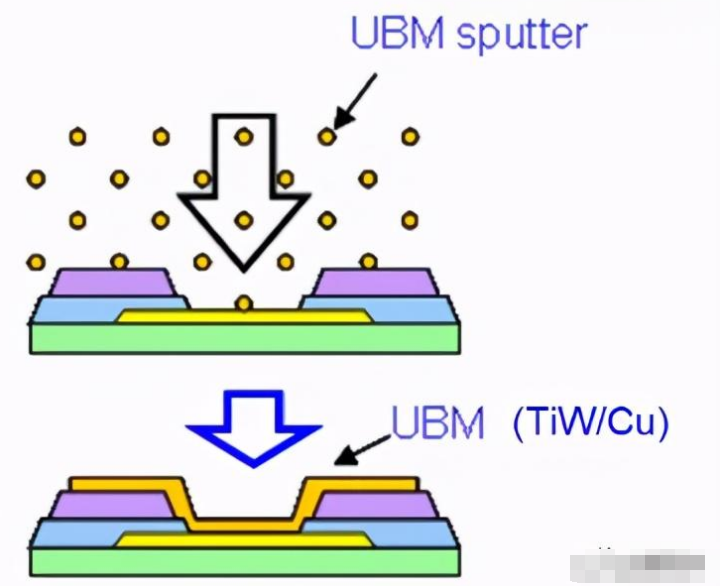

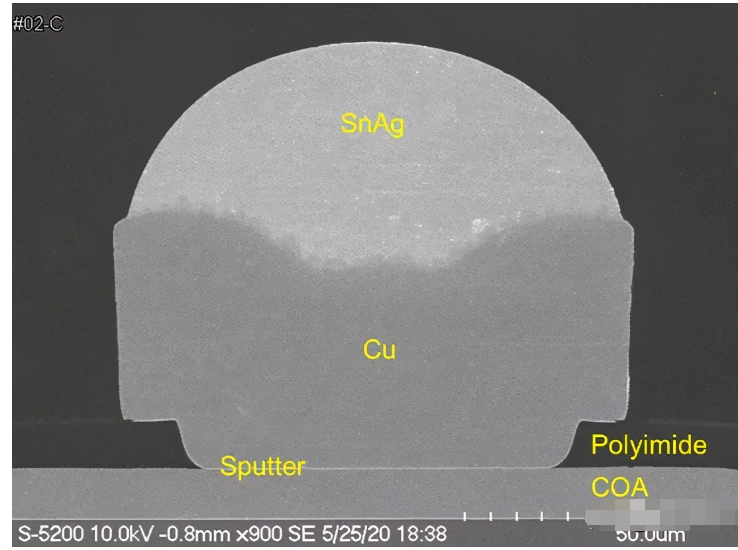

完成了前序動作,才真正開始bump制程,首先在incoming的wafer上濺鍍上一層薄薄的金屬層,一般是3um-[Ti](http://www.elecfans.com/tags/%E5%BE%B7%E5%B7%9E%E4%BB%AA%E5%99%A8/)w和2um-Cu,為fab的電路提供保護層并為fab和bump之間創建金屬互連層。

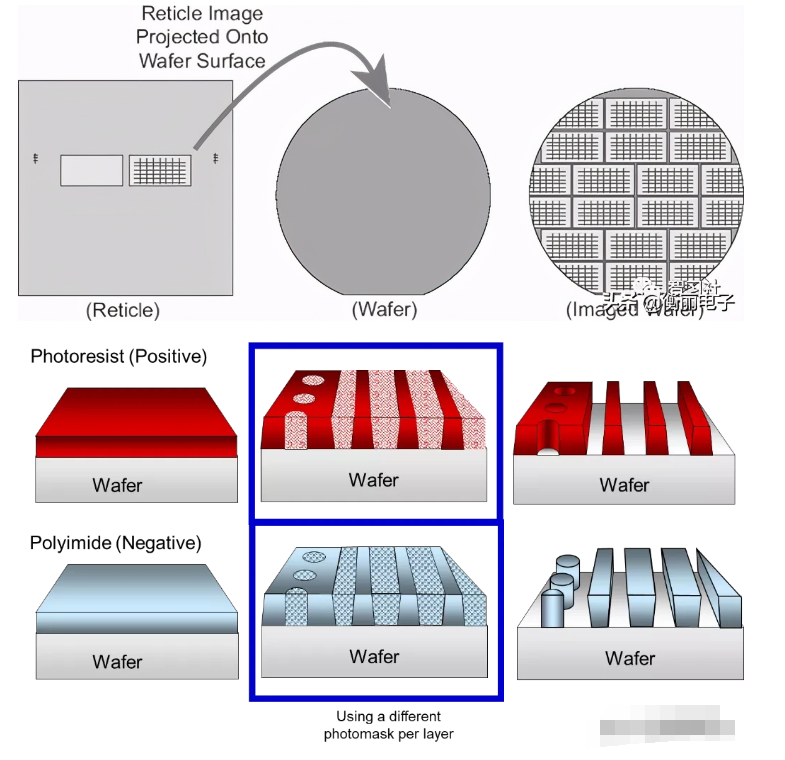

濺鍍完一層金屬薄膜之后整片wafer都是導電的,不能直接進行[電鍍](http://www.hqpcb.com/),需要先鋪光阻做圖案,只露出需要電鍍的區域并將不需要電鍍的地方保護起來,這個過程稱為photo制程。Photo制程分為鋪光阻、曝光、顯影,先將整片wafer鋪上光阻(光阻分為正性光阻和負性光阻,其區別在于被光照過的地方是易溶解還是不易溶解),然后利用帶有所需圖形的光照板進行曝光后得到所需的圖形,曝光所用的機臺就是我們常聽到的光刻機,不同機臺的功能一樣,只是原理有所不同,光刻機的精度直接影響芯片的尺寸大小以及一定尺寸下芯片電路的復雜程度。光阻經過曝光,會使得有些地方易于被顯影液溶解,有些地方則不易被溶解,因此經過顯影之后需要電鍍的地方就會被裸露出來。

光阻鋪完接下來則是電鍍,常用的電鍍方法有掛鍍法和垂直鍍法,目前采用的大多是垂直鍍法,電鍍的原理簡單來說就是銅離子失去電子得到銅并在電場的作用下沉積在wafer表面,根據給定的[電流](http://www.elecfans.com/tags/%E7%94%B5%E6%B5%81/)密度和電鍍時間控制電鍍銅的高度。BOAC是電鍍CU+Ni+Pb,也只電鍍一層金屬,而HOTROD和BOPCOA這一層metal為重分布層(COA/RDL),還需重復一次sput[te](http://www.elecfans.com/tags/te/)r+photo+plating制程,另外通常在兩層金屬之間會加一層polyimide進行防護。常規HOTROD制程的SnAg是直接通過電鍍完成然后進行reflow,而HOTROD-LITE和BOPCOA在電鍍過程中只鍍Cu,SnAg是通過ballattach+reflow完成的。

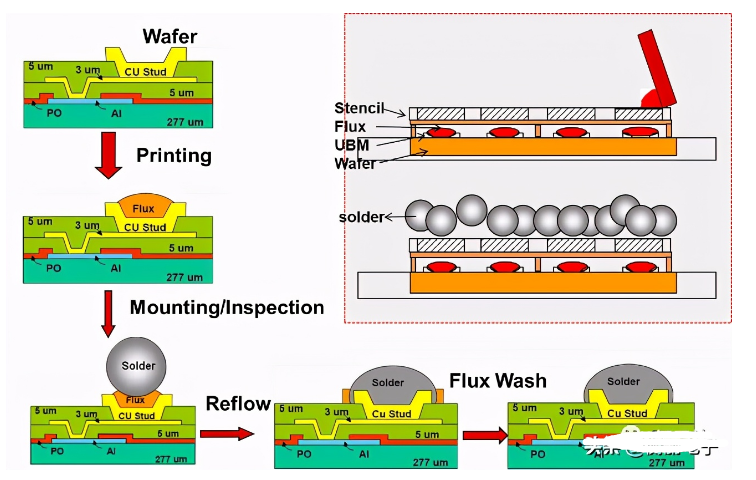

下圖為BOPCOA制程進行Ballattach的詳細過程:先在wafer表面涂上助焊劑,然后將錫銀球通過stencil置于對應的UBM上,然后經過reflow完成solder的植球過程。下圖給出為實際的bump結構的SEM-cut圖。

- 電子元器件

- 電阻

- 電容器

- 電感

- 保險絲

- 二極管

- 三極管

- 接插件

- 蜂鳴器

- MOS

- 集成電器基礎知識

- 接地的基礎知識

- STA

- Skew

- setup和hold

- 問題

- timing path

- Latency

- 跨時鐘域的代碼檢查(spyglass)

- 時間換算

- 名詞解釋

- 寄存器

- 觸發器

- ECO

- 通用芯片和嵌入式芯片有什么區別

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 邏輯閾值

- Floorplan

- 寄存器傳輸的設計(RTL)

- 集成電路設計方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片設計

- 什么是Scenario?

- 晶圓BUMP加工工藝和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency與delay區別

- Power

- LVT, RVT, HVT 的區別

- PPA

- RTL

- 芯片行業的IP是指什么?

- 晶振與晶體的區別

- PLL (鎖相環(PhaseLockedLoop))

- 奇偶分頻電路

- inverter

- glitch (電子脈沖)

- Power

- Clock Gating

- 低功耗設計

- UPF

- 低功耗單元庫

- Power intent

- 亞穩態

- 芯片流程

- 芯片軟件

- 亞穩態&MTBF&同步器&AFIFO

- glitch free的時鐘切換技術

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生電路?

- 晶振

- 信號完整性

- 什么是脈沖?什么是電平?

- 閾值電壓

- bump

- IC設計常用文件及格式介紹

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI簡介

- 異步橋

- 芯片后仿之SDF

- 慕課-VLSI設計基礎(數字集成電路設計基礎)

- 概論

- MOS晶體管原理

- 設計與工藝接口

- 反相器和組合邏輯電路

- 問題trainning