https://baijiahao.baidu.com/s?id=1704133260569135703&wfr=spider&for=pc

芯片行業中所說的IP,一般也稱為IP核。IP核是指芯片中具有獨立功能的電路模塊的成熟設計。該電路模塊設計可以應用在包含該電路模塊的其他芯片設計項目中,從而減少設計工作量,縮短設計周期,提高芯片設計的成功率。該電路模塊的成熟設計凝聚著設計者的智慧,體現了設計者的知識產權,因此,芯片行業就用IP核(Intellectual Property Core)來表示這種電路模塊的成熟設計。IP核也可以理解為芯片設計的中間構件。

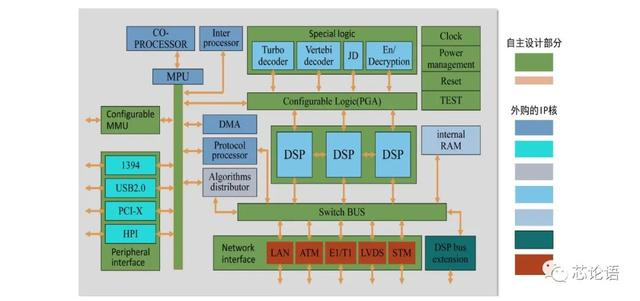

一般說來,一個復雜的芯片是由芯片設計者自主設計的電路部分和多個外購的IP核連接構成的。如圖2所示,要設計這樣結構的一款芯片,設計公司可以外購芯片中所有的IP核(不同顏色模塊),僅設計芯片中自己有創意的、自主設計的部分(用綠色表示),并把各部分連接起來。

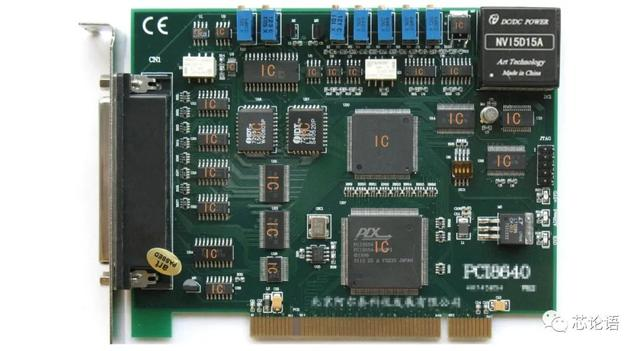

芯片設計過程就像圖3的系統電路板開發過程一樣,是用已有的、成熟的IP核(或者芯片)進行布局、擺放和信號連接的過程,這種過程可以稱為對IP核(或者芯片)的復用。不同的是,系統電路板上除了芯片和連接線之外,系統開發者很少自主開發自己的芯片。而在芯片設計過程中,芯片上除了采用外購的IP核之外,一般說來,芯片設計者還要設計一部分自己的電路,并完成各部分之間的信號連線,最后還要對整個芯片的功能、性能進行制造前的反復檢查和驗證。

IP核被其他芯片設計公司采用,行業內稱為IP復用。專門設計相對獨立電路功能模塊,目的是推廣給其他芯片設計公司進行復用,這種設計工作稱為IP開發。專門從事IP開發的公司稱為IP廠商,或者IP提供商。IP廠商把IP銷售給芯片設計公司是一種IP交易行為。

隨著現代信息社會對芯片要求提升,芯片的規模呈指數性增加,復雜性急劇增大。中小型芯片公司要獨立完成一款復雜芯片設計幾乎變得不太可能。特別是20世紀80年代末,芯片行業出現了晶圓代工(Foundry)商業模式,大批的中小微芯片設計公司(Fabless)應運而生。這個時期,芯片設計行業急需解決小芯片公司無法設計大芯片的難題。

IP的作用主要有四個方面,一是使芯片設計化繁為簡,縮短芯片設計周期,提高復雜芯片設計的成功率。二是IP開發和IP復用技術使小公司設計大芯片成為可能;三是使系統整機企業可以設計自己的芯片,提升自主創新能力和整機系統的自主知識產權含量;四是使芯片設計行業擺脫傳統IDM模式,成為產業鏈上獨立的行業,促進了芯片設計業迅猛發展。

IP核有行為(Behavior)級、結構(Structure)級和物理(Physical)級三個層次的分類,對應著三個種類型的IP核,它們是由硬件描述語言設計的軟核(Soft IP Core)、完成結構描述的固核(Firm IP Core)和基于物理描述并經過工藝驗證的硬核(Hard IP Core)。

1.IP軟核:它是用硬件描述語言(HDL)設計的獨立功能的電路模塊。從芯片設計程度來看,它只經過了RTL級設計優化和功能驗證,通常是以HDL文本形式提交給用戶。所以它不包含任何物理實現信息,因此,IP軟核與制造工藝無關。

用戶購買了IP軟核后,可以綜合出正確的門電路級設計網表,并可以進行后續的結構設計,具有很大的靈活性。借助于EDA綜合工具,用戶可以很容易與其它IP軟核,以及自主設計的電路部分合成一體,并根據各種不同半導體工藝,設計成具有不同性能的芯片。

2.IP固核:它的設計程度介于IP軟核和IP硬核之間,它除了完成IP軟核所有的設計外,還完成了門級電路綜合和時序仿真等設計環節。一般地,它以門級電路網表的形式提供給用戶。

3.IP硬核:它提供了電路設計最后階段掩模級的電路模塊。它以最終完成的布局布線網表形式提供給用戶。IP硬核既具有結果的可預見性,也可以針對特定工藝或特定IP提供商進行功耗和尺寸的優化。

芯片設計過程包括了行為級、結構級和物理級三個階段。行為級和結構級設計階段的工作一般稱為前端設計,物理級設計階段的工作一般稱為后端設計

芯片行業中所說的IP,也稱為IP核。IP核是指芯片中具有獨立功能的電路模塊的成熟設計。在電路模塊設計的三個不同階段,可以得到的不同類型的IP核,分別稱為IP軟核、IP固核和IP硬核。由軟化到固化,再到硬化,IP核的可配置性和靈活性變小,但完善性提高,復用風險性降低。芯片設計公司購買IP廠商的IP核,通過IP復用可以快速設計出功能復雜的芯片,可以節約設計時間,提高芯片設計成功率。IP開發和IP復用技術大大促進了芯片設計業的快速發展。

- 電子元器件

- 電阻

- 電容器

- 電感

- 保險絲

- 二極管

- 三極管

- 接插件

- 蜂鳴器

- MOS

- 集成電器基礎知識

- 接地的基礎知識

- STA

- Skew

- setup和hold

- 問題

- timing path

- Latency

- 跨時鐘域的代碼檢查(spyglass)

- 時間換算

- 名詞解釋

- 寄存器

- 觸發器

- ECO

- 通用芯片和嵌入式芯片有什么區別

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 邏輯閾值

- Floorplan

- 寄存器傳輸的設計(RTL)

- 集成電路設計方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片設計

- 什么是Scenario?

- 晶圓BUMP加工工藝和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency與delay區別

- Power

- LVT, RVT, HVT 的區別

- PPA

- RTL

- 芯片行業的IP是指什么?

- 晶振與晶體的區別

- PLL (鎖相環(PhaseLockedLoop))

- 奇偶分頻電路

- inverter

- glitch (電子脈沖)

- Power

- Clock Gating

- 低功耗設計

- UPF

- 低功耗單元庫

- Power intent

- 亞穩態

- 芯片流程

- 芯片軟件

- 亞穩態&MTBF&同步器&AFIFO

- glitch free的時鐘切換技術

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生電路?

- 晶振

- 信號完整性

- 什么是脈沖?什么是電平?

- 閾值電壓

- bump

- IC設計常用文件及格式介紹

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI簡介

- 異步橋

- 芯片后仿之SDF

- 慕課-VLSI設計基礎(數字集成電路設計基礎)

- 概論

- MOS晶體管原理

- 設計與工藝接口

- 反相器和組合邏輯電路

- 問題trainning