在搞芯片設計的公司,而且那個時候公司還買了很多STM32F411的“die”回來自己封裝,然后絲印搞上公司的產品,這樣就“完美”成為公司的芯片了。

“die”算是一個半成品,如果量大,自己買“die”來封裝成芯片,其實單價比買成品還要便宜(之前公司就是這樣考慮的,可惜···)。

最開始聽他們說“die”我都還不知道是什么意思,后來才知道原來芯片還可以這么搞。

下面就來說說wafer、die、cell這幾個專業名詞。

什么是waferwafer,即大家所說的“晶圓”,晶圓是指制作硅半導體電路所用的硅晶片,其原始材料是硅。

## wafer

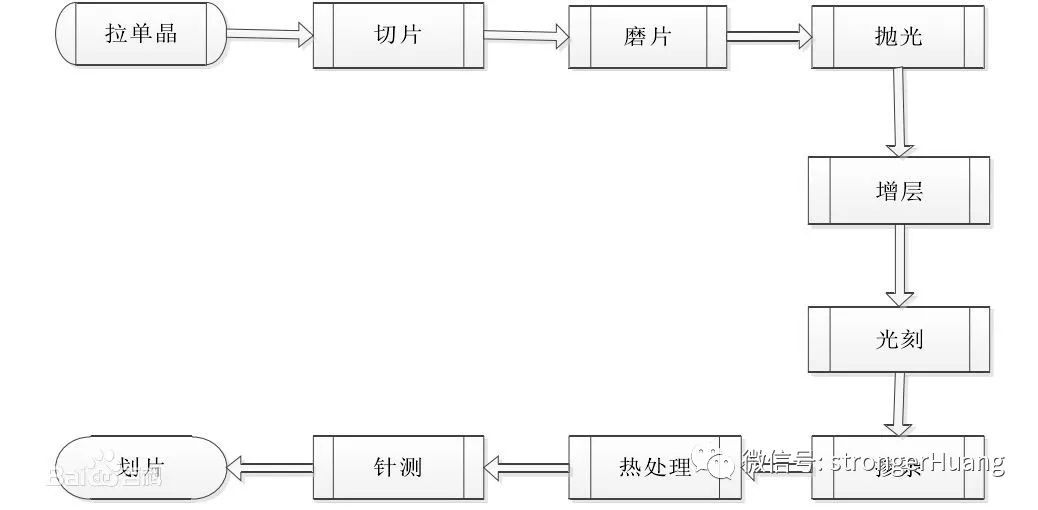

高純度的多晶硅溶解后摻入硅晶體晶種,然后慢慢拉出,形成圓柱形的單晶硅。硅晶棒在經過研磨,拋光,切片后,形成硅晶圓片,也就是晶圓。

目前國內晶圓生產線以8英寸和12英寸為主。

晶圓的主要加工方式為片加工和批加工,即同時加工1片或多片晶圓。隨著半導體特征尺寸越來越小,加工及測量設備越來越先進,使得晶圓加工出現了新的數據特點。

同時,特征尺寸的減小,使得晶圓加工時,空氣中的顆粒數對晶圓加工后質量及可靠性的影響增大,而隨著潔凈的提高,顆粒數也出現了新的數據特點。

## die

什么是die可能有人英語學得好,認為die不就是死亡的意思嗎。還有在百度百科中指的是芯片(die泛指為“芯片”)。

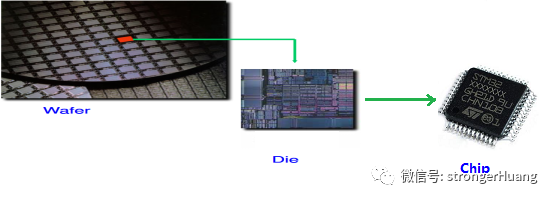

這里說的die指的是晶粒,即晶圓被切割切成的小塊,這里學名叫die。

die是硅片中一個很小的單位,包括了設計完整的單個芯片以及芯片鄰近水平和垂直方向上的部分劃片槽區域。

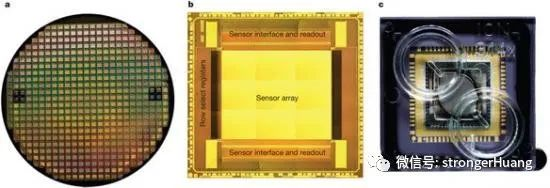

我們解剖芯片之后,就能看見芯片中的die:

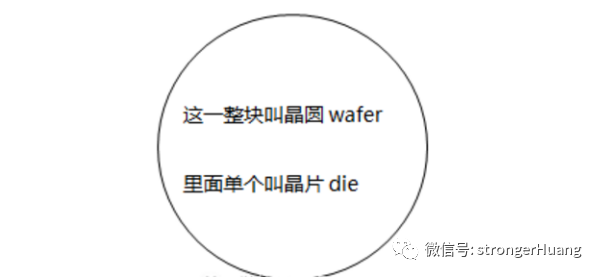

wafer和die的關系好比下面這張圖:

## cell

cell在集成電路中的解釋為“單元”,比die還要更小級別,通常有這么一個關系:wafer》die》cell

我這里也沒有找到明確的解釋,翻譯過來就是細胞、單元的意思,我大概看的解釋為:把die進一步劃分為多個cell,比如IO單元、電源管理單元等。

它們的關系和區別wafer為晶圓,由純硅(Si)構成。一般分為6英寸、8英寸、12英寸規格不等,晶片基于wafer上生產出來。Wafer上一個小塊晶片晶圓體學名die,封裝后成為一個顆粒。

一片載有NandFlash晶圓的wafer首先經過切割,測試后將完好的、穩定的、足容量的die取下,封裝形成日常所見的NandFlash芯片。

wafer和die的關系可以通過一張圖來理解:

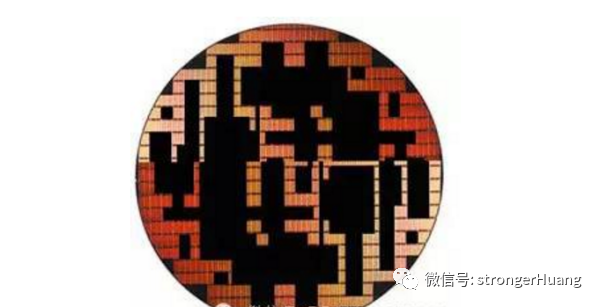

品質合格的die切割下去后,原來的晶圓成了下圖的樣子,是挑剩下的DowngradeFlashWafer。殘余的die是品質不合格的晶圓。黑色的部分是合格的die,會被原廠封裝制作為成品NAND顆粒,而不合格的部分,也就是圖中留下的部分則當做廢品處理掉。

篩選后的wafer

①材料來源方面的區別以硅工藝為例,一般把整片的硅片叫做wafer,通過工藝流程后每一個單元會被劃片,封裝。在封裝前的單個單元的裸片叫做die。chip是對芯片的泛稱,有時特指封裝好的芯片。

②品質方面的區別品質合格的die切割下去后,原來的晶圓就成了下圖的樣子,就是挑剩下的DowngradeFlashWafer。這些殘余的die,其實是品質不合格的晶圓。被摳走的部分,也就是黑色的部分,是合格的die,會被原廠封裝制作為成品NAND顆粒,而不合格的部分,也就是圖中留下的部分則當做廢品處理掉。

③大小方面的區別封裝前的單個單元的裸片叫做die。chip是對芯片的泛稱,有時特指封裝好的芯片。cell也是單元,但是比die更加小cell《die《chip。

- 電子元器件

- 電阻

- 電容器

- 電感

- 保險絲

- 二極管

- 三極管

- 接插件

- 蜂鳴器

- MOS

- 集成電器基礎知識

- 接地的基礎知識

- STA

- Skew

- setup和hold

- 問題

- timing path

- Latency

- 跨時鐘域的代碼檢查(spyglass)

- 時間換算

- 名詞解釋

- 寄存器

- 觸發器

- ECO

- 通用芯片和嵌入式芯片有什么區別

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 邏輯閾值

- Floorplan

- 寄存器傳輸的設計(RTL)

- 集成電路設計方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片設計

- 什么是Scenario?

- 晶圓BUMP加工工藝和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency與delay區別

- Power

- LVT, RVT, HVT 的區別

- PPA

- RTL

- 芯片行業的IP是指什么?

- 晶振與晶體的區別

- PLL (鎖相環(PhaseLockedLoop))

- 奇偶分頻電路

- inverter

- glitch (電子脈沖)

- Power

- Clock Gating

- 低功耗設計

- UPF

- 低功耗單元庫

- Power intent

- 亞穩態

- 芯片流程

- 芯片軟件

- 亞穩態&MTBF&同步器&AFIFO

- glitch free的時鐘切換技術

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生電路?

- 晶振

- 信號完整性

- 什么是脈沖?什么是電平?

- 閾值電壓

- bump

- IC設計常用文件及格式介紹

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI簡介

- 異步橋

- 芯片后仿之SDF

- 慕課-VLSI設計基礎(數字集成電路設計基礎)

- 概論

- MOS晶體管原理

- 設計與工藝接口

- 反相器和組合邏輯電路

- 問題trainning