[TOC]

# 前言

` `system verilog的仿真軟件基本都要license,并且環境安裝起來比較復雜。

` `在這里搭建VCS+Verdi環境用于仿真system verilog。

# 安裝vcs+verdi

## vcs2016安裝文件結構

–synopsys_installer #此程序用于安裝下面三個程序。所以你想安裝VCS,Verdi,SCL的任意一個,都需要這個文件。

–vcs_2016

–verdi_2016

–scl_11.9?? ?#此程序統一管理license等破解文件

–scl_keygen #這個是破解程序(放在windows下的)。此文件用于生成license文件

## 軟件包

[vcs2016](https://pan.baidu.com/s/1AHsMVCQ0So9K6opBmJlBWw) 提取碼: hpta

## 解壓相關壓縮包

` `synopsys_installer是rar格式壓縮包,可以在Windows下先解壓。之后把四個文件夾:synopsys_installer、vcs_2016、verdi_2016、scl_v11.9傳到deepin linux上。

## 安裝synopsys installer

` `將對應的安裝包下載解壓之后,現在我們需要在Ubuntu里面安裝synopsys installer,之后通過synopsys installer安裝scl、verdi、vcs。

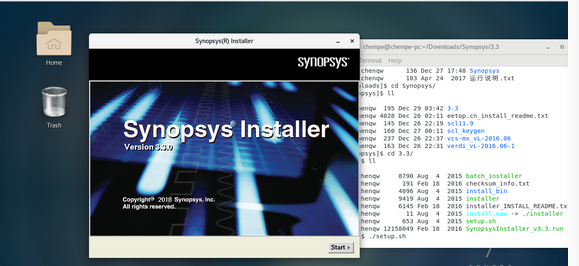

(1)解壓后的synopsys_installer文件夾里有:

–checksum_info.txt

–installer_INSTALL_README.txt

–SynopsysInstaller_v3.3.run (可執行文件)

(2)在Deepin的shell環境下運行SynopsysInstaller_v3.3.run

? command:

~~~bash

./SynopsysInstaller_v3.3.run

~~~

(3)第二步后得到在同一文件夾等到setup.sh文件。

## 建立相關文件夾

` `在第三步我們有了setup.sh文件,之后就是安裝vcs, verdi, scl了

` `但是首先,必須先給這三個建立屬于自己的文件夾。

command:

~~~bash

mkdir synopsys ? ? ? #這個是建一個總文件夾cd synopsys ? ? ? ? #切換到該文件夾?mkdir vcs_2016.06 #為vcs建立文件夾mkdir scl_11.9 #為scl建立文件夾mkdir verdi_2016.06-1 #為verdi建立文件夾

~~~

## 啟動synopsys installer并安裝

` `在第三步synopsys installer文件夾下我們得到setup.sh文件,切換到該文件夾下執行該文件

command:

~~~bash

cd synopsys_installer./setup.sh

~~~

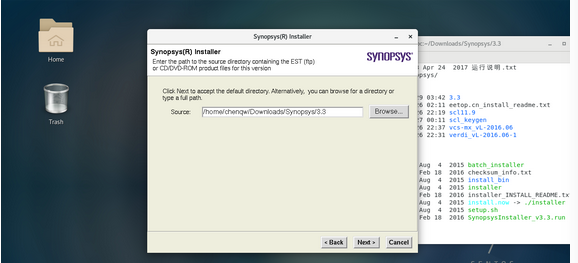

` `點擊Start,有幾個選項,什么站點信息,郵箱,名字,隨便填就好了。Next后,得到

` `這個Browse就是找到vcs, verdi, scl的位置。我們在第二步不是把vcs, verdi, scl三個軟件的包傳到Deepin上了嗎。此時Browse就是找到這個我們需要安裝的那個軟件的軟件包地址。

` `在這里,vcs、verdi、scl安裝步驟是一樣的,以vcs為例。

` `點擊Browse后,選中第二步存放VCS的那個文件夾之后,點擊Done–>Next。

` `接下來選擇與自己系統相對應的版本選擇安裝,途中需要選擇安裝路徑,選擇在第4步建好的相應的文件夾,并且等待成功安裝即可。

## window上或者使用wine獲得license

以上5步便已經安裝完畢了,但是,并沒有license,所以不能打開軟件。這個時候,就要用到scl_keygen這個文件夾了。

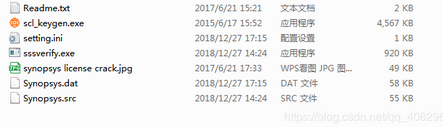

scl_keygen文件夾有:

` `使用deepin-wine打開scl_keygen.exe。

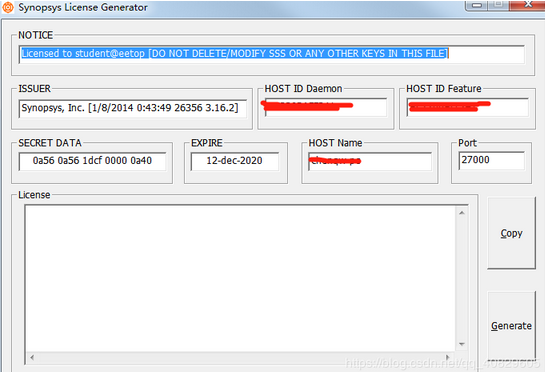

` `只需要修改以上涂黑的三項:HOST ID Deamon、HOST ID Feature、HOST_Name

` `其中HOST ID Deamon和HOST ID Feature填的是一樣的,HOST_Name填自己主機的名字。

**那怎么查看具體填什么?**

1、HOST ID Deamon和HOST_Name查看方法:

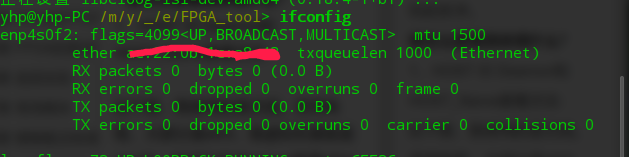

如下圖,我使用的是無線。若用電纜,大部分是eth0,我虛擬機里面是ens33。HOST ID Deamon就是ether后面紅色覆蓋的12個字符(冒號除外);比如ether 00:0a:21:51:12:4w。則HOST ID Deamon就是:000a2151124w

2、HOST_Name可以直接在終端輸入hostname獲得

~~~bash

hostname #直接在Terminal的shell里面輸入

~~~

` `填好之后,直接點擊Generate。在同一個文件夾就會出現Synopsys.dat。這個就是我們要的文件了。

## 修改Synopsys.dat文件并復制到對應文件夾

` `之前說過scl是一個統一管理Synopsys軟件license的軟件。

1、修改Synopsys.dat:

將第二行 修改成DAEMON snpslmd ?/home/路徑/synopsys/scl_11.9/amd64/bin/snpslmd (這是你snpslmd對應的路徑,修改成你自己的)

那怎么查看自己的snpslmd對應的路徑?

在第五步安裝SCL時,我們選擇了一個目錄去安裝它。切換到SCL安裝目錄。然后用命令去查找snpslmd文件:

~~~bash

find ./ -name snpslmd

~~~

返回的就是snpslmd相對于現在目錄的相對路徑。我們再加上前面路徑即可(直接pwd查看前面路徑)

2、文件復制:

將Synopsys.dat文件復制到…/synopsys/vcs_2016.06/license/和…/synopsys/verdi_2016/license/兩個文件夾中(這是你license對應的路徑,修改成你自己的,如沒有license文件夾,自己建即可)。

## 設置環境變量

```

#dve

export PATH=$PATH:/home/chenqw/synopsys/vcs_2016.06/gui/dve/bin #改成自己vcs的安裝路徑

alias dve=“dve -full64”

#VCS

export PATH=$PATH:/home/chenqw/synopsys/vcs_2016.06/bin #改成自己vcs的安裝路徑

alias vcs="vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed" #vcs需要的固定的參數,注意系統要安裝gcc-4.8和g++-4.8,這兩個需要自己獨立安裝

#VERDI

export PATH=$PATH:/home/chenqw/synopsys/verdi_2016.06-1/bin #改Verdi安裝路徑

export VCS_HOME=/home/chenqw/synopsys/vcs_2016.06

export VERDI_HOME=/home/chenqw/synopsys/verdi_2016.06-1

export NOVAS_HOME=/home/chenqw/synopsys/verdi_2016.06-1

#LICENCE

export LM_LICENSE_FILE=27000@chenqw-pc #這個chenqw-pc改成自己的host name

alias lmg_vcs=“lmgrd -c /home/chenqw/synopsys/vcs_2016.06/license/Synopsys.dat” #注意改路徑

#scl

export PATH=$PATH:/home/chenqw/synopsys/scl_11.9/linux/bin #改SCL安裝路徑

export VCS_ARCH_OVERRIDE=linux

```

以上的配置僅作參考,需要根據你的安裝路徑進行配置。

之后使配置文件立即生效即可:

~~~bash

source .bashrc

~~~

## 激活

激活license是最關鍵的步驟。在之前可能需要安裝:

~~~bash

sudo apt-get install lsb-core ? #lsb-core

上述不可以時嘗試使用

sudo apt-get install lsb-compat

~~~

因為激活的端口使用的是27000。我實現開放了此端口。開放端口的方法可自行百度。

接下來直接在終端輸入

~~~bash

lmg_vcs

~~~

等待激活即可。

1、若途中有關TCP port的報錯,查詢27000端口進程,直接kill 掉等待27000端口完全釋放再重新lmg\_vcs即可。

command:

sudo netstat -ap | grep 27000

kill -9 \*\*\*\*\*\*

2、Failed to open the TCP port number in the license問題:

如果遇到這個問題,可以在Terminal輸入:lmdown

然后會問y/n,輸入y。然后等待一會兒就可以了。注意要等待一會兒

參考:[http://bbs.eetop.cn/thread-307403-3-1.html](http://bbs.eetop.cn/thread-307403-3-1.html)

3、lmgrd can't make directory /usr/tmp/.flexlm when running server on Ubuntu問題:

這個問題,可以參考這個鏈接[http://www.myir-tech.com/faq\_list.asp?id=521](http://www.myir-tech.com/faq_list.asp?id=521)

就是:

```

sudo -i #切換到root權限

mkdir /usr/tmp/ #創建目錄(Ubuntu下沒有這個目錄)

chmod 777 /usr/tmp/ #修改權限

```

lmdown一遍,等待一會兒,再重新lmg_vcs竟然好了。

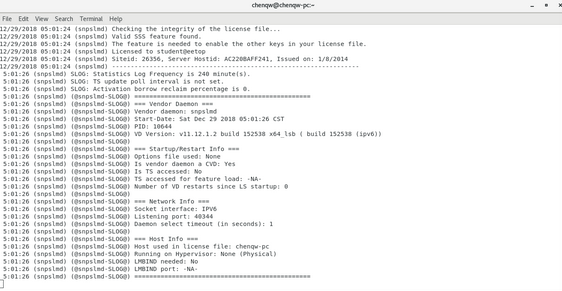

如果你看到你的輸出最下面幾行和這個文件可以對應,就成功了。Enter一下就OK。

## 運行dve, vcs ,verdi

### 1、啟動dve

~~~bash

dve #啟動vcs圖形界面

~~~

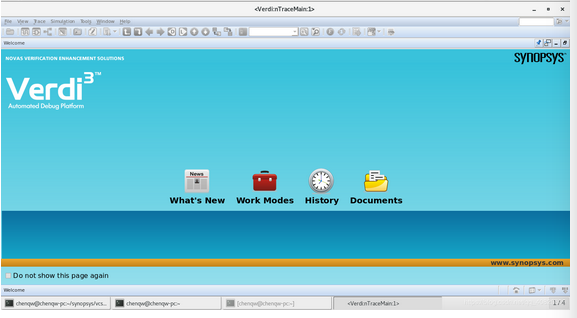

### 2、啟動verdi:

~~~bash

verdi #啟動verdi

~~~

1、在啟動verdi時,可能會出現一個語法錯誤:

verdi_2016/bin/verdi: 433: /home/book/synopsysoftware/verdi_2016/bin/verdi: Syntax error: "(" unexpected

解決:

進入verdi安裝目錄下的/bin目錄,里面有一個verdi的腳本,把這個腳本第433行的那個function去掉。

2、可能有些32位的共享包沒有安裝的情況,比如:libjpeg.so.62: cannot open shared object file: No such file or directory。

~~~

sudo apt install libjpeg62

~~~

3、或者是libpng12.so.0: cannot open shared object file: No such file or directory

```

sudo -i #先進入root權限

wget -q -O /tmp/libpng12.deb http://mirrors.kernel.org/ubuntu/pool/main/libp/libpng/libpng12-0_1.2.54-1ubuntu1_amd64.deb

> && dpkg -i /tmp/libpng12.deb \

> && rm /tmp/libpng12.deb

#用wget得到相應的包

```

一切問題解決后,再返回到用戶狀態,執行:

## 使用

注意,在每重啟一遍機器,想要運行dve或verdi之前,都要先運行

~~~bash

lmg_vcs

~~~

這個命令成功后,方可運行vcs和verdi.

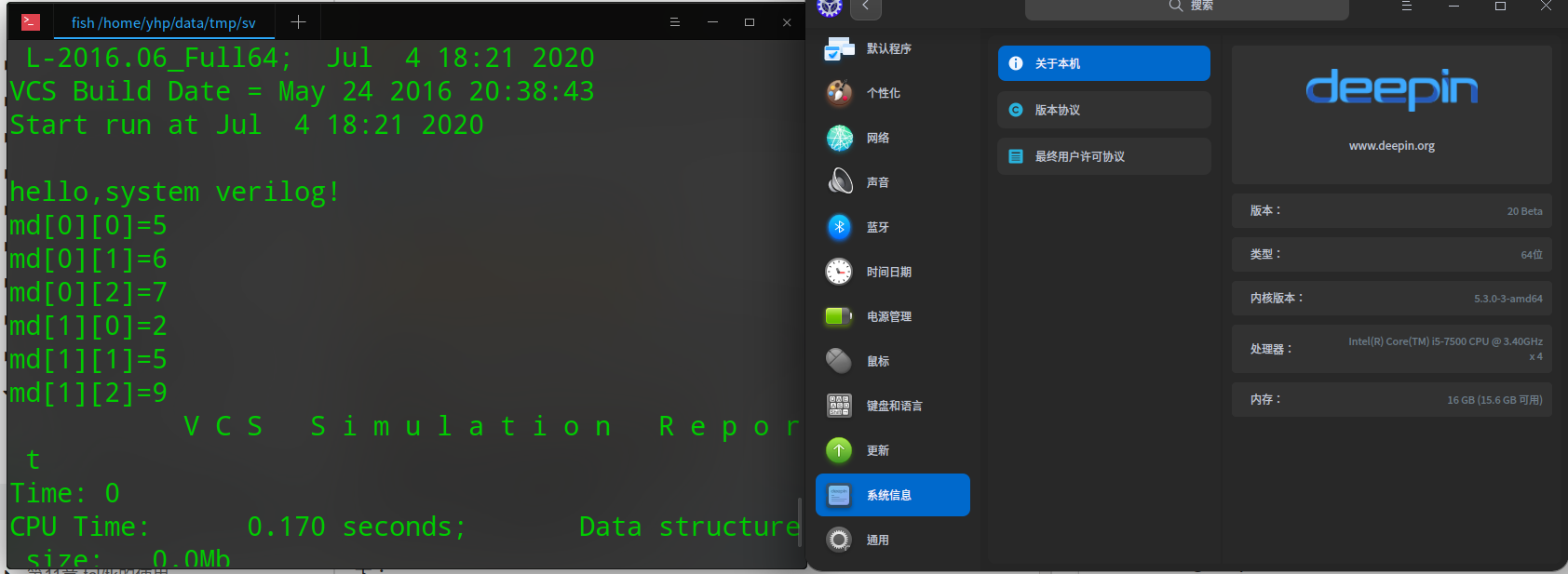

# 上述方法可以在deepin v20中使用

已經驗證過,但是需要注意的是有一些小問題,做以下記錄:

**問題1:**

**問題2:安裝lsb-core失敗,軟件倉庫中沒有**

換用deepin 15.110的軟件源后再安裝。

**問題3:fish shell下的配置**

在fish shell下配置環境變量,需要更改文件 `~/.config/fish/config.fish`,我的更改如下:

```

####------ 配置 vcs -----------

#dve

set -x PATH $PATH /home/yhp/data/exsoft/vcs/vcs-mx_vL-2016.06/gui/dve/bin #改成自己vcs的安裝路徑

alias dve="dve -full64"

#VCS

set -x PATH $PATH /home/yhp/data/exsoft/vcs/vcs-mx_vL-2016.06/bin #改成自己vcs的安裝路徑

alias vcs="vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed" #vcs需要的固定的參數,注意系統要安裝gcc-4.8和g++-4.8,這兩個需要自己獨立安裝

#VERDI

set -x PATH $PATH /home/yhp/data/exsoft/vcs/verdi_vL-2016.06-1/bin #改Verdi安裝路徑

set -x VCS_HOME /home/yhp/data/exsoft/vcs/vcs-mx_vL-2016.06

set -x VERDI_HOME /home/yhp/data/exsoft/vcs/verdi_vL-2016.06-1

set -x NOVAS_HOME /home/yhp/data/exsoft/vcs/verdi_vL-2016.06-1

#LICENCE

set -x LM_LICENSE_FILE 27000@yhp-PC #這個chenqw-pc改成自己的host name

alias lmg_vcs="lmgrd -c /home/yhp/data/exsoft/vcs/vcs-mx_vL-2016.06/license/Synopsys.dat" #注意改路徑

#scl

set -x PATH $PATH /home/yhp/data/exsoft/vcs/scl_v11.9/amd64/bin #改SCL安裝路徑

set -x VCS_ARCH_OVERRIDE linux

###----------------------------

```

- 序

- 第1章 Linux下開發FPGA

- 1.1 Linux下安裝diamond

- 1.2 使用輕量級linux仿真工具iverilog

- 1.3 使用linux shell來讀寫串口

- 1.4 嵌入式上的linux

- 設備數教程

- linux C 標準庫文檔

- linux 網絡編程

- 開機啟動流程

- 1.5 linux上實現與樹莓派,FPGA等通信的串口腳本

- 第2章 Intel FPGA的使用

- 2.1 特別注意

- 2.2 高級應用開發流程

- 2.2.1 生成二進制bit流rbf

- 2.2.2 制作Preloader Image

- 2.2.2.1 生成BSP文件

- 2.2.2.2 編譯preloader和uboot

- 2.2.2.3 更新SD的preloader和uboot

- 2.3 HPS使用

- 2.3.1 通過JTAG下載代碼

- 2.3.2 HPS軟件部分開發

- 2.3 quartus中IP核的使用

- 2.3.1 Intel中RS232串口IP的使用

- 2.4 一些問題的解決方法

- 2.4.1 關于引腳的復用的綜合出錯

- 第3章 關于C/C++的一些語法

- 3.1 C中數組作為形參不傳長度

- 3.2 匯編中JUMP和CALL的區別

- 3.3 c++中map的使用

- 3.4 鏈表的一些應用

- 3.5 vector的使用

- 3.6 使用C實現一個簡單的FIFO

- 3.6.1 循環隊列

- 3.7 C語言不定長參數

- 3.8 AD采樣計算同頻信號的相位差

- 3.9 使用C實現棧

- 3.10 增量式PID

- 第4章 Xilinx的FPGA使用

- 4.1 Alinx使用中的一些問題及解決方法

- 4.1.1 在Genarate Bitstream時提示沒有name.tcl

- 4.1.2 利用verilog求位寬

- 4.1.3 vivado中AXI寫DDR說明

- 4.1.4 zynq中AXI GPIO中斷問題

- 4.1.5 關于時序約束

- 4.1.6 zynq的PS端利用串口接收電腦的數據

- 4.1.7 SDK啟動出錯的解決方法

- 4.1.8 讓工具綜合是不優化某一模塊的方法

- 4.1.9 固化程序(雙核)

- 4.1.10 分配引腳時的問題

- 4.1.11 vivado仿真時相對文件路徑的問題

- 4.2 GCC使用Attribute分配空間給變量

- 4.3 關于Zynq的DDR寫入byte和word的方法

- 4.4 常用模塊

- 4.4.1 I2S接收串轉并

- 4.5 時鐘約束

- 4.5.1 時鐘約束

- 4.6 VIVADO使用

- 4.6.1 使用vivado進行仿真

- 4.7 關于PicoBlaze軟核的使用

- 4.8 vivado一些IP的使用

- 4.8.1 float-point浮點單元的使用

- 4.10 zynq的雙核中斷

- 第5章 FPGA的那些好用的工具

- 5.1 iverilog

- 5.2 Arduino串口繪圖器工具

- 5.3 LabVIEW

- 5.4 FPGA開發實用小工具

- 5.5 Linux下繪制時序圖軟件

- 5.6 verilog和VHDL相互轉換工具

- 5.7 linux下搭建輕量易用的verilog仿真環境

- 5.8 VCS仿真verilog并查看波形

- 5.9 Verilog開源的綜合工具-Yosys

- 5.10 sublim text3編輯器配置verilog編輯環境

- 5.11 在線工具

- 真值表 -> 邏輯表達式

- 5.12 Modelsim使用命令仿真

- 5.13 使用TCL實現的個人仿真腳本

- 5.14 在cygwin下使用命令行下載arduino代碼到開發板

- 5.15 STM32開發

- 5.15.1 安裝Atollic TrueSTUDIO for STM32

- 5.15.2 LED閃爍吧

- 5.15.3 模擬U盤

- 第6章 底層實現

- 6.1 硬件實現加法的流程

- 6.2 硬件實現乘法器

- 6.3 UART實現

- 6.3.1 通用串口發送模塊

- 6.4 二進制數轉BCD碼

- 6.5 基本開源資源

- 6.5.1 深度資源

- 6.5.2 FreeCore資源集合

- 第7章 常用模塊

- 7.1 溫濕度傳感器DHT11的verilog驅動

- 7.2 DAC7631驅動(verilog)

- 7.3 按鍵消抖

- 7.4 小腳丫數碼管顯示

- 7.5 verilog實現任意人數表決器

- 7.6 基本模塊head.v

- 7.7 四相八拍步進電機驅動

- 7.8 單片機部分

- 7.8.1 I2C OLED驅動

- 第8章 verilog 掃盲區

- 8.1 時序電路中數據的讀寫

- 8.2 從RTL角度來看verilog中=和<=的區別

- 8.3 case和casez的區別

- 8.4 關于參數的傳遞與讀取(paramter)

- 8.5 關于符號優先級

- 第9章 verilog中的一些語法使用

- 9.1 可綜合的repeat

- 第10章 system verilog

- 10.1 簡介

- 10.2 推薦demo學習網址

- 10.3 VCS在linux上環境的搭建

- 10.4 deepin15.11(linux)下搭建system verilog的vcs仿真環境

- 10.5 linux上使用vcs寫的腳本仿真管理

- 10.6 system verilog基本語法

- 10.6.1 數據類型

- 10.6.2 枚舉與字符串

- 第11章 tcl/tk的使用

- 11.1 使用Tcl/Tk

- 11.2 tcl基本語法教程

- 11.3 Tk的基本語法

- 11.3.1 建立按鈕

- 11.3.2 復選框

- 11.3.3 單選框

- 11.3.4 標簽

- 11.3.5 建立信息

- 11.3.6 建立輸入框

- 11.3.7 旋轉框

- 11.3.8 框架

- 11.3.9 標簽框架

- 11.3.10 將窗口小部件分配到框架/標簽框架

- 11.3.11 建立新的上層窗口

- 11.3.12 建立菜單

- 11.3.13 上層窗口建立菜單

- 11.3.14 建立滾動條

- 11.4 窗口管理器

- 11.5 一些學習的腳本

- 11.6 一些常用的操作語法實現

- 11.6.1 刪除同一后綴的文件

- 11.7 在Lattice的Diamond中使用tcl

- 第12章 FPGA的重要知識

- 12.1 面積與速度的平衡與互換

- 12.2 硬件原則

- 12.3 系統原則

- 12.4 同步設計原則

- 12.5 乒乓操作

- 12.6 串并轉換設計技巧

- 12.7 流水線操作設計思想

- 12.8 數據接口的同步方法

- 第13章 小項目

- 13.1 數字濾波器

- 13.2 FIFO

- 13.3 一個精簡的CPU( mini-mcu )

- 13.3.1 基本功能實現

- 13.3.2 中斷添加

- 13.3.3 使用中斷實現流水燈(實際硬件驗證)

- 13.3.4 綜合一點的應用示例

- 13.4.5 使用flex開發匯編編譯器

- 13.4.5 linux--Flex and Bison

- 13.4 有符號數轉單精度浮點數

- 13.5 串口調試FPGA模板